# CENTRO DE INVESTIGACIÓN CIENTÍFICA Y DE EDUCACIÓN SUPERIOR DE ENSENADA

# PROGRAMA DE POSGRADO EN CIENCIAS EN ELECTRÓNICA Y TELECOMUNICACIONES

#### MODELADO DE TRANSISTORES DE POTENCIA A BASE DE GaN

#### **TESIS**

que para cubrir parcialmente los requisitos necesarios para obtener el grado de MAESTRO EN CIENCIAS

Presenta:

ANDRÉS ZÁRATE DE LANDA

Ensenada, Baja California, México, Agosto 2007

**RESUMEN** de la tesis de **Andrés Zárate de Landa**, presentada como requisito parcial para la obtención del grado de MAESTRO EN CIENCIAS en ELECTRÓNICA Y TELECOMUNCACIONES con orientación en Electrónica de Alta Frecuencia. Ensenada, Baja California, México. Agosto 2007.

#### MODELADO DE TRANSISTORES DE POTENCIA A BASE DE GaN.

| Resumen | apro | bado | por: |

|---------|------|------|------|

|---------|------|------|------|

Dr. J. Apolinar Reynoso Hernández Director de Tesis

El transistor de alta movilidad electrónica (HEMT) basado en AlGaN/GaN es un serio candidato para aplicaciones de microondas debido a su alta potencia y características de bajo ruido a tales frecuencias. El diseño de amplificadores de potencia de AlGaN/GaN requiere de un modelo en gran señal del dispositivo. El modelo en gran señal está basado en el modelo de pequeña señal obtenido a diferentes condiciones de polarización. Además, para el análisis del comportamiento de ruido se requiere del conocimiento del modelo en pequeña señal para extraer el modelo intrínseco de ruido.

El circuito equivalente en pequeña señal utilizado para modelar MESFETs de GaAs y PHEMTs consiste de elementos parásitos e intrínsecos. Existe un método bien establecido para extraer los elementos parásitos para este tipo de transistor, conocido como método de "cold FET" (FET en frío). En el caso de HEMTs de AlGaN/GaN los elementos parásitos del modelo de circuito equivalente en pequeña señal son difíciles de extraer utilizando el método del "cold FET", particularmente la resistencia de compuerta R<sub>g</sub> y la inductancia de compuerta L<sub>g</sub>. La dificultad reside en que se necesitan valores muy altos de corriente de compuerta en directo para suprimir el efecto de la resistencia diferencial de compuerta, sin embargo, altas corrientes de compuerta en directo pueden producir daños irreversibles en esta y dañar al dispositivo.

En este trabajo de tesis se presenta un nuevo método para extraer las resistencias e inductancias parásitas al polarizar el HEMT de AlGaN/GaN con bajos valores de corriente de DC de compuerta en directo y drenador flotante. La originalidad del método propuesto recae en el uso de una baja corriente de DC de compuerta en directo para extraer  $R_g$  y  $L_g$ , mientras que el método clásico para extraer  $R_g$  y  $L_g$  utiliza diferentes conjuntos de parámetros S medidos a altas corrientes de DC de compuerta en directo. Además, se presenta un método sencillo para calcular las capacitancias parásitas  $C_{pg}$  y  $C_{pd}$  al restar a la medición del "cold FET" bloqueado las inductancias parásitas de compuerta y drenador, y tomando en cuenta la capacitancia del diodo Schottky. Se verifica la validez del método propuesto por la buena predicción del modelo de los datos experimentales.

**Palabras Clave**: AlGaN/GaN HEMTs, elementos parásitos, circuito eléctrico equivalente de pequeña señal.

**ABSTRACT** of the thesis presented by **Andrés Zárate de Landa** as a partial requirement to obtain the MASTER OF SCIENCE degree in ELECTRONICS AND TELECOMMUNICATIONS majoring in high frequency electronics. Ensenada, Baja California, Mexico. August 2007.

#### MODELING OF GaN BASED POWER TRANSISTORS.

The AlGaN/GaN high electron-mobility transistor (HEMT) is a promising candidate for microwave applications due to its high power and low noise characteristics at such frequencies. Power AlGaN/GaN amplifier design requires large-signal modeling of the device. The large-signal model is based on small-signal models derived at different bias conditions. In addition, noise performance analysis also requires the knowledge of the small-signal model in order to extract the intrinsic noise parameters.

The small signal equivalent circuit used for modeling GaAs MESFETs and PHEMTs consists of parasitic and intrinsic elements. For this kind of transistor, and using large DC forward current, a well established method for extracting parasitic resistances and inductances already exists. In the case of AlGaN/GaN HEMTs the parasitic elements of the small-signal equivalent circuit are still difficult to extract. It's well known that the gate resistance  $R_{\rm g}$  and gate inductance  $L_{\rm g}$  are very difficult to extract using the cold-FET method. The difficulty lies in the fact that a very high forward gate current is needed to suppress the gate differential resistance. However, large gate forward currents could produce irreversible and catastrophic damage to the transistor gate.

By biasing the AlGaN/GaN HEMTs with a low DC gate forward current and a floating drain, a new method for extracting parasitic resistances and parasitic inductances is introduced. The originality of the proposed method lies in the low DC gate forward current used for extracting  $R_g$  and  $L_g$ . While the classical method for extracting  $R_g$  and  $L_g$  uses a set of S-parameters measured under different large DC gate forward current, the proposed method uses a data set of S-parameters measured at a single low DC gate forward current. Also, by de-embedding the parasitic gate and drain inductances from the pinchoff "cold FET" measurement, and taking into account the Schottky diode capacitance a very easy method for extracting the parasitic capacitances  $C_{pg}$  and  $C_{pd}$  is presented. The excellent agreement between the model and experimental data verifies the validity of the proposed method.

**Keywords:** AlGaN/GaN HEMTs, parasitic elements, small-signal equivalent circuit.

...A mis padres por su apoyo incondicional

#### **Agradecimientos**

A mis papas Martha y Ramón por que gracias a ellos y a su ejemplo soy la persona que soy ahora y sobre todo por aguantarme todos estos años.

A mi hermana Alejandra y a mi cuñado Joey por su apoyo incondicional.

Le agradezco a mi director de tesis Dr. J. Apolinar Reynoso por que en este año de tesis más que un profesor fue un amigo y por todas las cosas que aprendí de él.

A los miembros de mi comité de tesis Dr. Héctor Escamilla, Dr. José Luís Medina y a la Dra. María del Carmen Maya por su tiempo y cuidadosa revisión de esta tesis.

A todos mis compañeros y amigos que hice en estos dos años de maestría con quienes pase momentos inolvidables.

A mis amigos Diana, Eric, Jesús, Ricardo, Adhara, Blanca, Arlethe, Gladis, Pau, Patty, quienes compartieron mis alegrías y tristezas como si fueran suyas y por su apoyo incondicional en todo lo que hago.

A mis profesores Apolinar Reynoso, José Luís Medina, Arturo Velázquez, Ricardo Chávez, Jesús Ibarra, Carmen Maya y Benjamín Ramírez por su paciencia, dedicación en enseñar y siempre estar disponibles para resolver dudas.

A Eleazar Zúñiga por enseñarme a utilizar el equipo de medición.

Al CONACYT por su apoyo financiero en mis estudios de maestría.

## Índice

| Capítulo I                                                                                                            |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| Introducción                                                                                                          | 1  |

| I.1 Antecedentes.                                                                                                     |    |

| I.2 Objetivo.                                                                                                         |    |

| I.3 Planteamiento del Problema.                                                                                       |    |

| I.4 Metodología de Investigación.                                                                                     |    |

| I.5 Organización de la Tesis.                                                                                         |    |

| Capítulo II                                                                                                           |    |

| Material Semiconductor de Nitruro de Galio                                                                            | 8  |

| II.1 Características de los Transistores de AlGaN/GaN.                                                                |    |

| II.2 Estado del Arte.                                                                                                 |    |

| II.3 Ventajas del Material Semiconductor de Nitruro de Galio                                                          |    |

| II.4 Origen de los electrones 2DEG.                                                                                   |    |

| II.5 Efectos de Alta Corriente y Limitaciones Carga-Espacio.                                                          |    |

| II.6 Efectos de Alto Voltaje.                                                                                         |    |

| II.7 Modo de Operación.                                                                                               |    |

| II.8 Aplicaciones.                                                                                                    |    |

| Capítulo III<br>Modelado de Transistores                                                                              |    |

| III.1 Importancia del Modelado de Transistores                                                                        |    |

| III.2 Métodos Para Determinar los Elementos Parásitos del Circuito Equivalente d                                      |    |

| de Pequeña Señal                                                                                                      |    |

| III.2.1 Resistencias e Inductancias Parásitas.                                                                        |    |

| III.2.1.1 Método en DC.                                                                                               |    |

| III.2.1.2 Métodos en RF ("cold FET")                                                                                  |    |

| III.2.1.2.2 Método del Cold FE1                                                                                       |    |

| III.2.1.2.3 Método de Giovanni Crupi et al.                                                                           |    |

| III.2.2 Capacitancias Parásitas (cold FET en pinchoff. $V_{gs} < V_p$ ; $V_{ds} = 0$ )                                |    |

| III.2.2 Capacitalicias i arasitas (cold i E i cli piliciloii. v <sub>gs</sub> < v <sub>p</sub> , v <sub>ds</sub> = 0) |    |

| III.2.2.2 Método de White.                                                                                            |    |

| III.2.2.3 Método de Chen et al.                                                                                       |    |

| III.2.3 Método de Jarndal y Kompa para calcular los elementos parásitos en                                            | 02 |

| dispositivos de GaN.                                                                                                  | 53 |

| III.2.4 Desventajas de los Métodos Existentes.                                                                        |    |

| III.2.4.1 Desventajas del Método de Dambrine et al.                                                                   |    |

## Índice (continuación)

| III.2.4.2 Desventajas del Método de Chen et al                                 |                          |

|--------------------------------------------------------------------------------|--------------------------|

| III.2.4.3 Desventajas del Método de Crupi et al.                               |                          |

| III.2.4.4 Desventajas del Método de Jarndal y Kompa                            |                          |

| III.3 Métodos Para Determinar los Elementos Intrínsecos del Circuito Equival   |                          |

| FET de Pequeña Señal (FET caliente)                                            |                          |

| III.3.1 Método de Dambrine.                                                    |                          |

| III.3.2 Método de Beroth y R. Bosh.                                            |                          |

| III.3.3 Jarndal y Kompa.                                                       |                          |

| III.4 Proceso de De-embedding.                                                 | 72                       |

| Capítulo IV                                                                    |                          |

| Nuevo Método para Extraer los Elementos Parásitos de                           |                          |

| Transistores de GaN en Oblea                                                   | 73                       |

| IV.1 Introducción.                                                             |                          |

| IV.2 Cálculo de las Resistencias e Inductancias Parásitas ("Cold FET" con Po   |                          |

| en Directo, $V_{gs} > V_{bi} > 0$ ; $V_{ds} = flotante$ )                      | 74                       |

| IV.2.1 Cálculo de las Inductancias Parásitas y la Capacitancia del Diodo So    | chottky C <sub>0</sub> . |

|                                                                                | 75                       |

| IV.2.2 Cálculo de las Resistencias Parásitas                                   |                          |

| IV.3 Cálculo de las Capacitancias Parásitas (Mediciones en Inverso)            |                          |

| IV.4 Cálculo de la Inductancia de Fuente L <sub>s</sub> Cuando es Menor a Cero | 85                       |

| Capítulo V                                                                     |                          |

| Resultados                                                                     | 87                       |

| V.1 Introducción.                                                              |                          |

| V.2 Extracción de los Elementos Parásitos.                                     | 87                       |

| V.2.1 Resistencias e Inductancias Parásitas                                    | 89                       |

| V.2.2 Capacitancias Parásitas.                                                 | 93                       |

| V.2.3 Conclusiones de la Extracción de los Elementos Parásitos                 |                          |

| V.3 Extracción de los Elementos Intrínsecos.                                   | 97                       |

| V.3.1 Transistor de 100μm.                                                     |                          |

| V.3.2 Transistor de 300μm.                                                     |                          |

| V.3.3 Transistor de 2mm.                                                       |                          |

| V.3.4 Conclusiones de la Extracción de los Elementos Intrínsecos               |                          |

| V.4 Aplicación del Método a Transistores de Diferentes Tecnologías.            |                          |

| V.4.1 Transistor HEMT de Fosfuro de Indio (InP).                               |                          |

| V.4.2 Transistor MESFET de Arseniuro de Galio (GaAs)                           |                          |

| V.4.3 Transistor HEMT de Carburo de Silicio (SiC).                             | 113                      |

## Índice (continuación)

| Capítulo VI                                                               |     |

|---------------------------------------------------------------------------|-----|

| Conclusiones                                                              | 115 |

| VI.1 Conclusiones                                                         |     |

| VI.3 Aportaciones                                                         |     |

| VI.2 Trabajo futuro                                                       |     |

| Referencias                                                               | 117 |

| Apéndice A                                                                | 120 |

| A.1 Analizador de Redes Vectorial HP5810.                                 |     |

| A.2 Máquina de Puntas Summit 9000.                                        |     |

| Apéndice B                                                                | 123 |

| B.1 Mediciones en Directa ( $V_{gs} > V_{bi} > 0$ ; $V_{ds} = flotante$ ) |     |

| B.2 Mediciones en Inversa $(V_{gs} < V_p; V_{ds} = 0)$                    |     |

| B 3 Mediciones a Diferentes Puntos de Polarización                        |     |

## Lista de Figuras

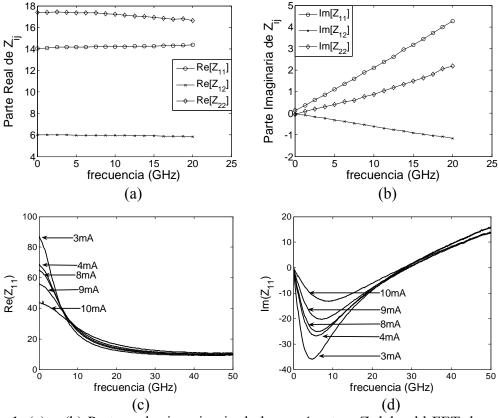

| Figura 1. (a) y (b) Parte real e imaginaria de los parámetros Z del cold-FET de un HEM de AlGaAs/GaAs. (c) y (d) Parte real e imaginaria de Z <sub>11</sub> de un HEMT de | Γ    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| AlGaN/GaN                                                                                                                                                                 | 5    |

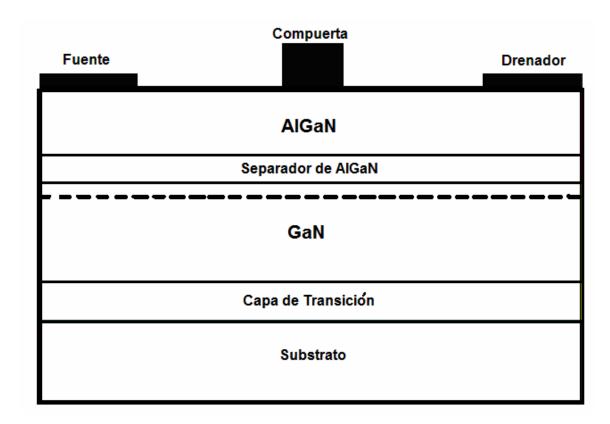

| Figura 2. Configuración del HEMT de AlGaN/GaN                                                                                                                             | . 12 |

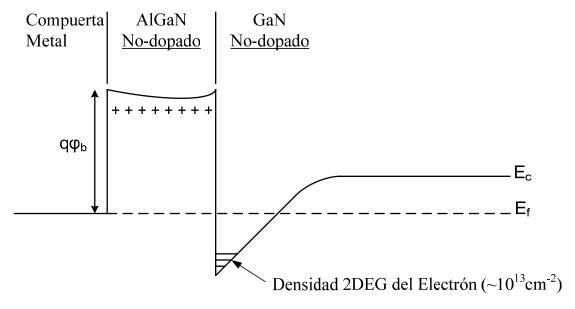

| Figura 3. Banda de conducción de una heterounión de AlGaN/GaN mostrando el pozo                                                                                           |      |

| quántico y 2DEG.                                                                                                                                                          | . 16 |

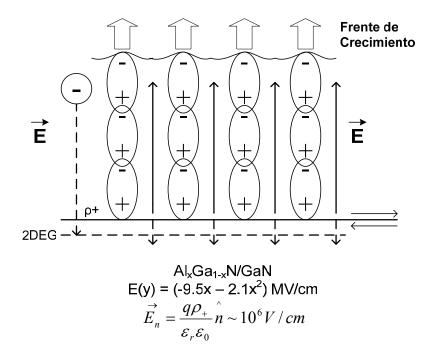

| Figura 4. Modelo de formación del gas bidimensional en la interfaz AlGaN/GaN                                                                                              | . 17 |

| Figura 5 Modo de operación de un FET de Silicio                                                                                                                           |      |

| Figura 6 Modo de operación de un FET de GaN                                                                                                                               | . 23 |

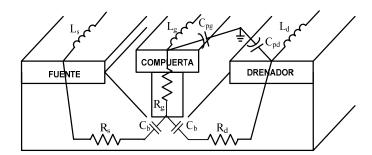

| Figura 7. Ubicación de los elementos del circuito eléctrico equivalente para un transistor                                                                                | r de |

| efecto de campo.                                                                                                                                                          | 27   |

| Figura 8. Modelo en gran señal del FET.                                                                                                                                   | 29   |

| Figura 9. Modelo de diodo Schottky para transistores con drenador o fuente flotante                                                                                       | . 31 |

| Figura 10. Modelo del circuito eléctrico equivalente del transistor propuesto por Dambri                                                                                  | ine. |

|                                                                                                                                                                           |      |

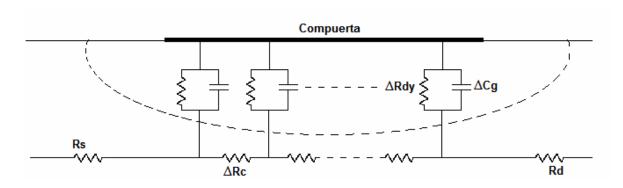

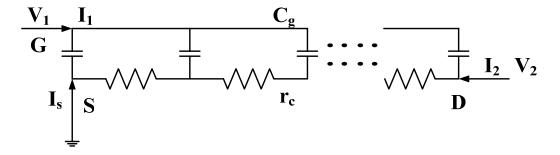

| Figura 11. Descripción de la red RC distribuida bajo la compuerta.                                                                                                        | . 39 |

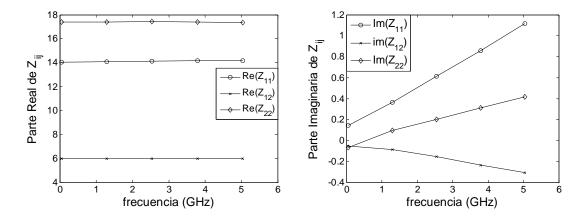

| Figura 12. Evolución de la parte real e imaginaria de los parámetros Z de un HEMT de                                                                                      |      |

| GaAs versus frecuencia bajo polarización directa en la compuerta y $V_{ds}$ = abien                                                                                       | rto. |

|                                                                                                                                                                           |      |

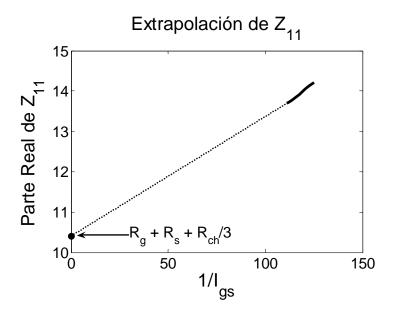

| Figura 13. Evolución de la parte real de $Z_{11}$ en función de $1/I_g$ .                                                                                                 | . 42 |

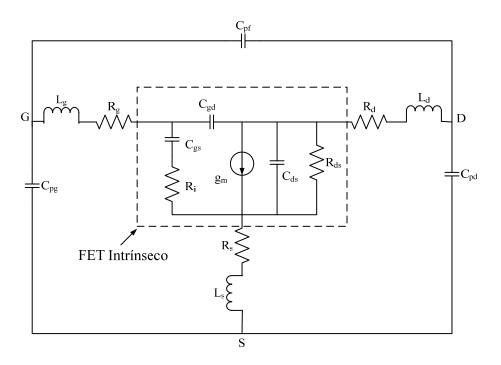

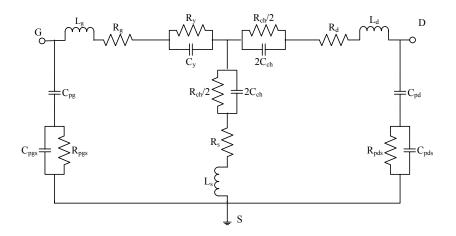

| Figura 14. Circuito eléctrico equivalente en pequeña señal de HEMTs de AlGaN/GaN                                                                                          |      |

|                                                                                                                                                                           | 43   |

| Figura 15. Circuito eléctrico equivalente del HEMT intrínseco de AlGaN/GaN a voltajes                                                                                     | s de |

| compuerta bajos y $V_{ds} = 0 V$                                                                                                                                          |      |

| Figura 16. Circuito equivalente del dispositivo.                                                                                                                          |      |

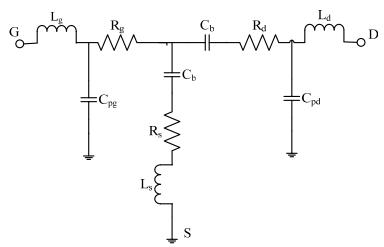

| Figura 17. Circuito equivalente del HEMT de GaN en "frío".                                                                                                                |      |

| Figura 18. Modelo de Dambrine de la zona de deserción debajo de la compuerta para el                                                                                      |      |

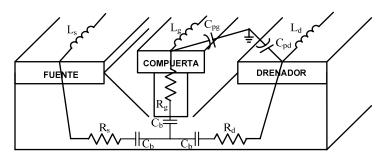

| "cold FET" en pinchoff                                                                                                                                                    |      |

| Figura 19. Circuito equivalente del "cold FET" en pinchoff según Dambrine                                                                                                 |      |

| Figura 20. Modelo de la zona de deserción debajo de la compuerta propuesto por White                                                                                      | 2.51 |

| Figura 21. Circuito equivalente de pequeña señal de un "cold FET" en pinchoff según                                                                                       |      |

| White                                                                                                                                                                     |      |

| Figura 22. Circuito eléctrico equivalente del dispositivo sin estructura de compuerta                                                                                     |      |

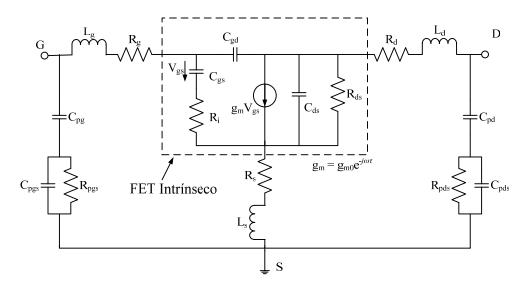

| Figura 23. Modelo del HEMT de GaN activo de 22 elementos.                                                                                                                 |      |

| Figura 24. Modelo del "cold FET" de GaN en pinchoff a baja frecuencia.                                                                                                    |      |

| Figura 25. Representa la red-T del circuito equivalente del "cold FET" en pinchoff                                                                                        |      |

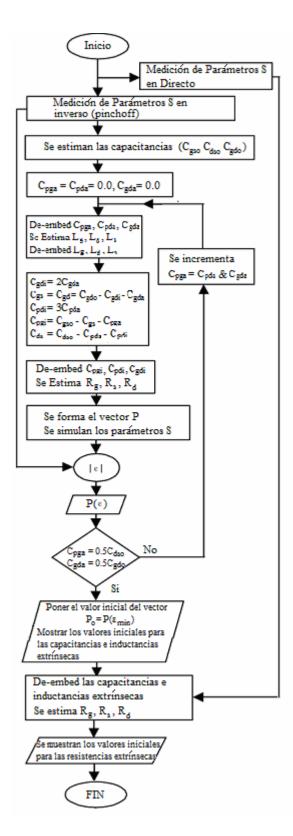

| Figura 26. Diagrama de flujo del algoritmo para el cálculo de los valores iniciales de los                                                                                |      |

| parámetros extrínsecos del modelo.                                                                                                                                        |      |

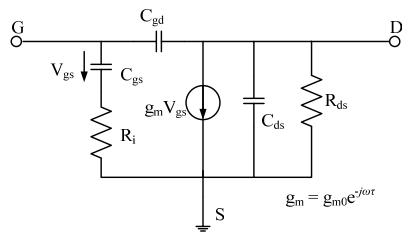

| Figura 27. Circuito eléctrico equivalente del transistor intrínseco propuesto por Dambrir                                                                                 |      |

|                                                                                                                                                                           | . 66 |

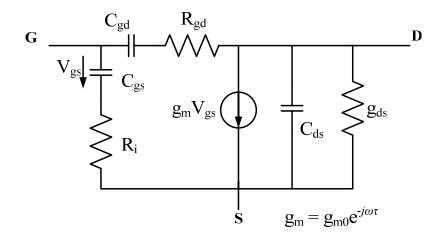

| Figura 28. Circuito eléctrico equivalente del transistor intrínseco propuesto por M. Berro                                                                                |      |

| v R. Bosh                                                                                                                                                                 | . 68 |

## Lista de Figuras (continuación)

| Figura 29. Proceso de de-embedding para el cálculo de los parámetros Y del transistor intrínseco.                                                                                                          | . 72         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

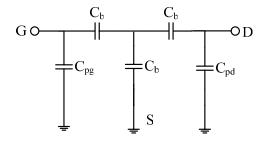

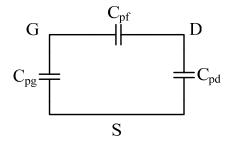

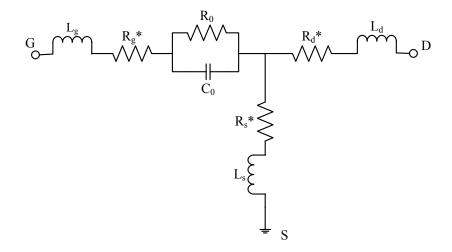

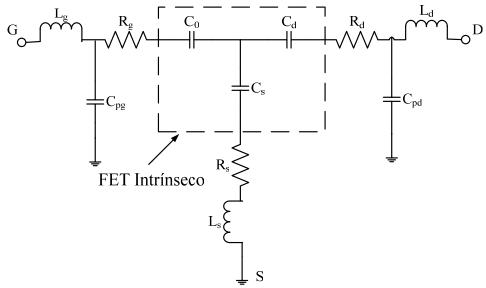

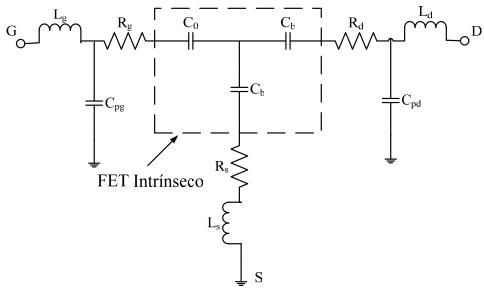

| Figura 30. Circuito eléctrico equivalente utilizado para modelar el HEMT en oblea Figura 31. Circuito equivalente del HEMT de GaN con corriente DC baja en directa en l compuerta y drenador flotante.     | . 74         |

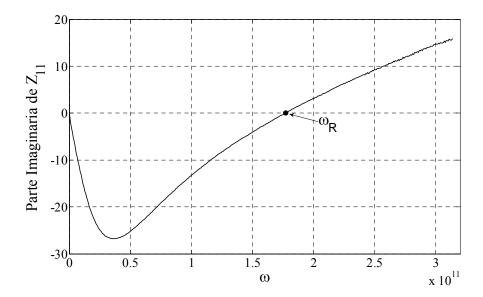

| Figura 32. Gráfica de la parte imaginaria de $Z_{11}$ donde se muestra la frecuencia de resonancia $\omega_R$ .                                                                                            | . 76         |

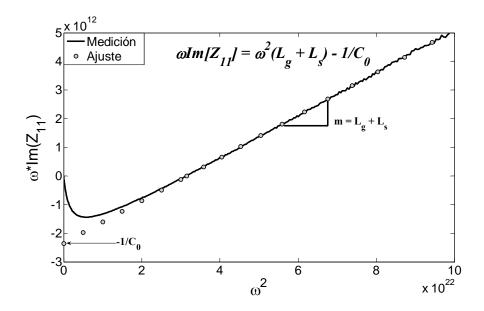

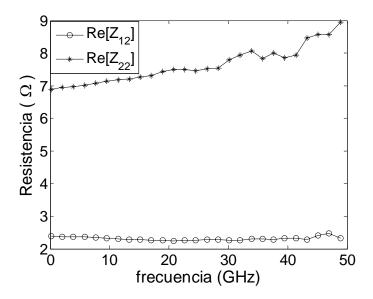

| Figura 33. Gráfica de $\omega$ Im[ $Z_{11}$ ] versus $\omega^2$ utilizada para calcular ( $L_g + L_s$ ) y $C_0$<br>Figura 34. Gráfica de la parte real de $Z_{12}$ y $Z_{22}$ versus frecuencia de un HEMT | . 77<br>. 78 |

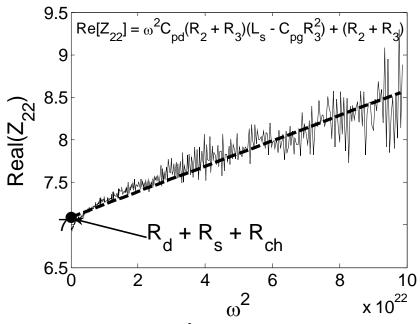

| Figura 35. Gráfica de Re(Z <sub>22</sub> ) versus ω <sup>2</sup> utilizada para extraer el valor de R <sub>d</sub> del transisto de AlGaN/GaN de 300 μm.                                                   | r<br>. 79    |

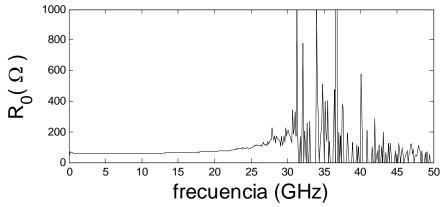

| Figura 36. Gráfica de $R_0$ versus frecuencia para un HEMT de GaN de $100\mu m$ . Figura 37. Circuito equivalente del transistor polarizado en Inverso con $V_{gs} << V_p$ y $V_{ds}$ =                    | = 0.         |

| Figura 38. Circuito equivalente del transistor polarizado en Inverso transformado a topología en T.                                                                                                        | . 82         |

| Figura 39. Circuito equivalente del transistor polarizado en Inverso definiendo la                                                                                                                         | . 83         |

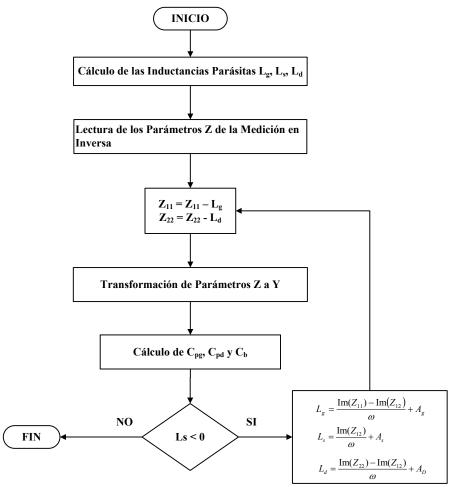

| Figura 40. Algoritmo para encontrar los valores óptimos de capacitancias e inductancias                                                                                                                    |              |

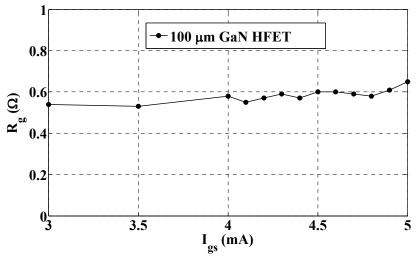

| Figura 41. Comportamiento de R <sub>g</sub> independiente de la polarización para el HEMT de Ga de 100 µm.                                                                                                 | aN<br>. 89   |

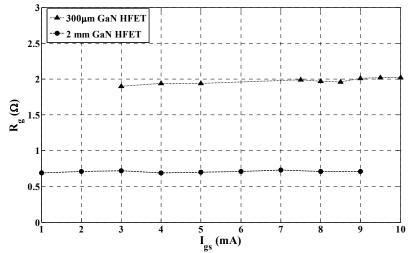

| Figura 42. Independencia con respecto a la polarización de R <sub>g</sub> para los HEMTs de GaN o 300 µm y 2mm.                                                                                            | de           |

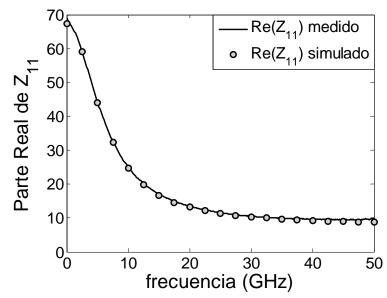

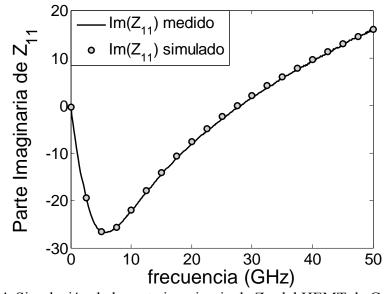

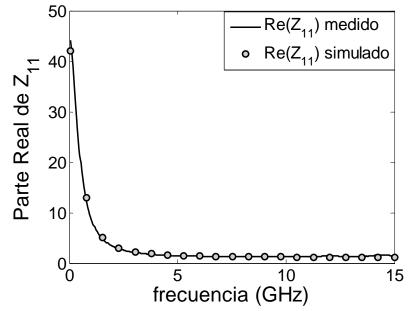

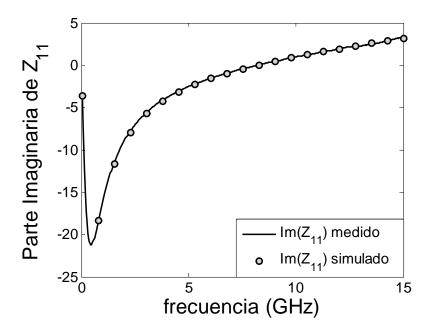

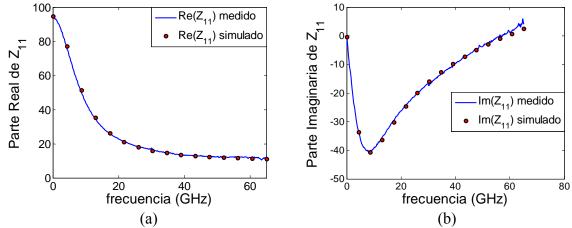

| Figura 43. Simulación de la parte real de Z <sub>11</sub> del HEMT de GaN de 100μm. Figura 44. Simulación de la parte imaginaria de Z <sub>11</sub> del HEMT de GaN de 100μm.                              | . 90         |

| Figura 45. Simulación de la parte real de $Z_{11}$ del HEMT de GaN de 300 $\mu$ m. Figura 46. Simulación de la parte imaginaria de $Z_{11}$ del HEMT de GaN de 300 $\mu$ m. Figura 46.                     | . 91         |

| Figura 47. Simulación de la parte real de Z <sub>11</sub> del HEMT de GaN de 2mm.                                                                                                                          | . 92         |

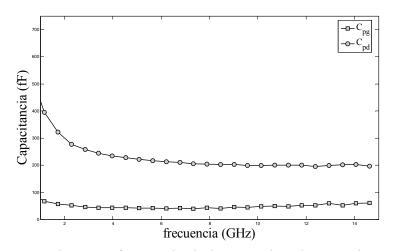

| Figura 48. Simulación de la parte imaginaria de Z <sub>11</sub> del HEMT de GaN de 2mm                                                                                                                     | 1            |

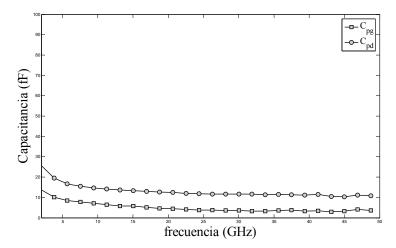

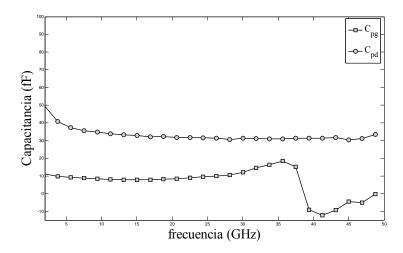

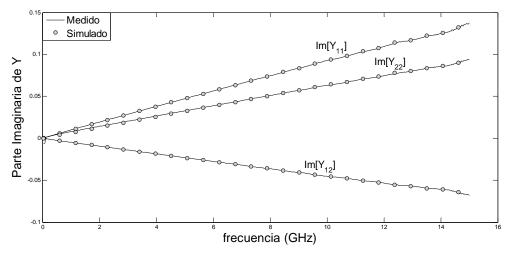

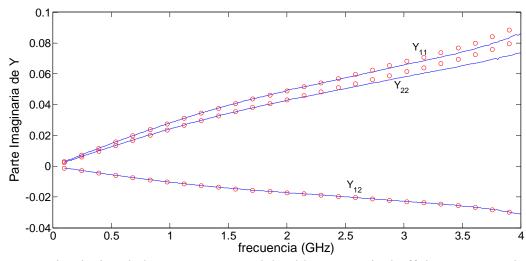

| Figura 50. Comportamiento en frecuencia de las capacitancias parásitas $C_{pg}$ y $C_{pd}$ para el transistor de $300\mu m$ .                                                                              | l<br>. 93    |

| Figura 51. Comportamiento en frecuencia de las capacitancias parásitas C <sub>pg</sub> y C <sub>pd</sub> para el transistor de 2mm.                                                                        |              |

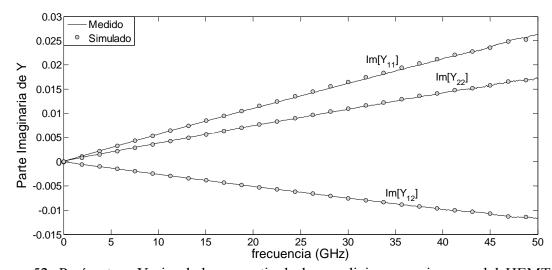

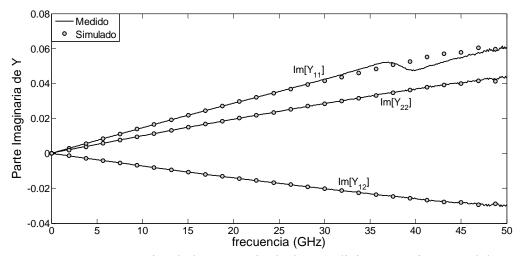

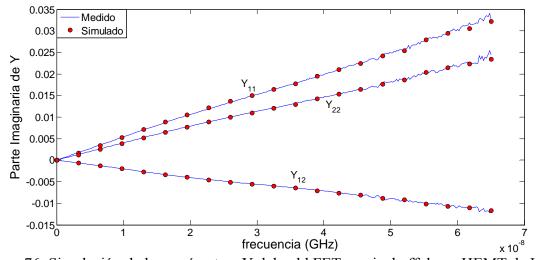

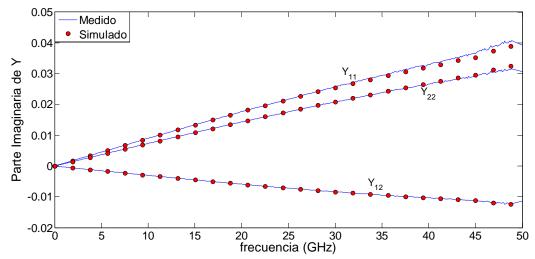

| Figura 52. Parámetros Y simulados a partir de las mediciones en inverso del HEMT de GaN de 100μm.                                                                                                          | . 95         |

| Figura 53. Parámetros Y simulados a partir de las mediciones en inverso del HEMT de GaN de 300µm                                                                                                           | 95           |

# Lista de Figuras (continuación)

| Figura 54. Parámetros Y simulados a partir de las mediciones en inverso del HEMT de GaN de 2mm                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

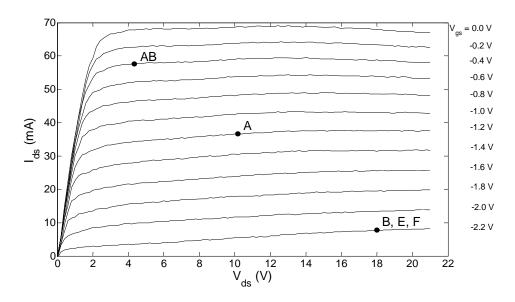

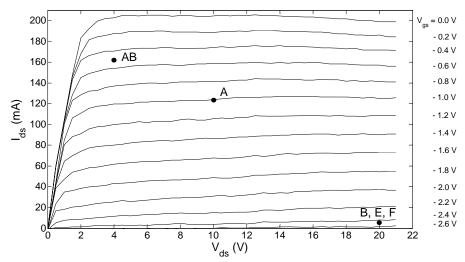

| Figura 55. Gráfica I(V) del HEMT de GaN de 100 μm y la ubicación de las diferentes polarizaciones para el diseño de amplificadores clase A, AB, B, E y F                                                    |

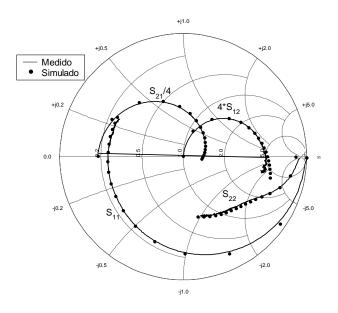

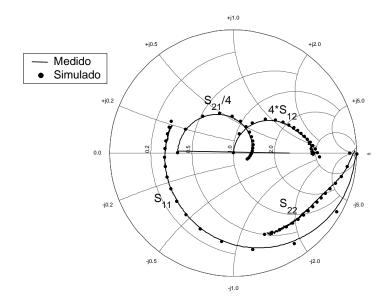

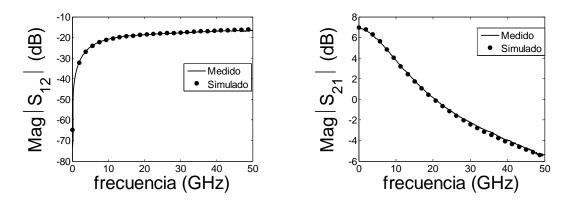

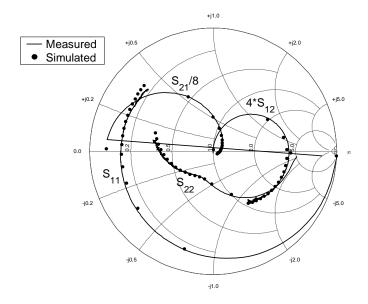

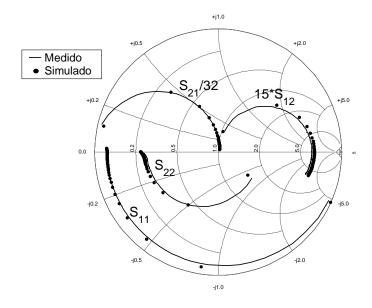

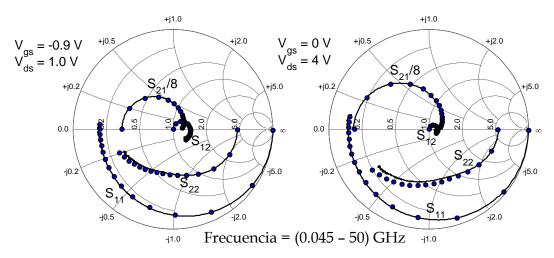

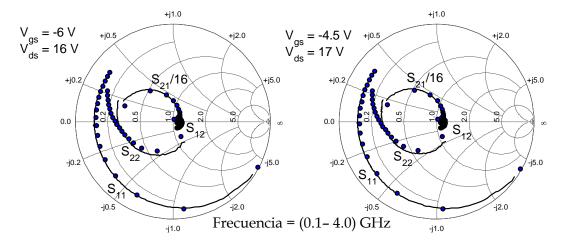

| Figura 56. Comparación de los parámetros S medidos y simulados a una polarización para el diseño de un amplificador clase A ( $V_{gs}$ = -1.2 V; $V_{ds}$ = 10.0 V; $I_{ds}$ = 36.6 mA).                    |

| Figura 57. Comparación de los parámetros S medidos y simulados a una polarización para el diseño de un amplificador clase B, E o F ( $V_{gs}$ = -2.2 V; $V_{ds}$ = 18.0 V; $I_{ds}$ = 4.2 mA)99             |

| Figura 58. Comparación de los parámetros $S$ medidos $y$ simulados a una polarización para el diseño de un amplificador clase $AB$ ( $V_{gs}$ = -0.4 $V$ ; $V_{ds}$ = 4.0 $V$ ; $I_{ds}$ = 57.48 mA)99      |

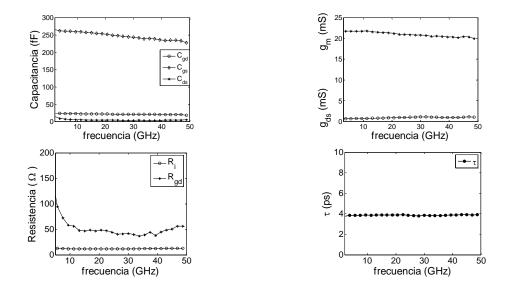

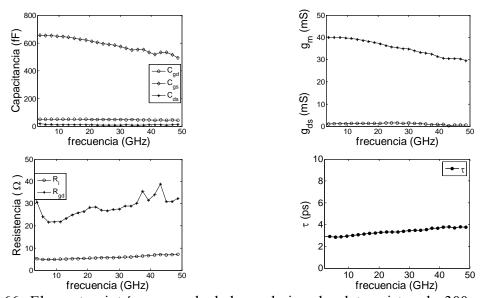

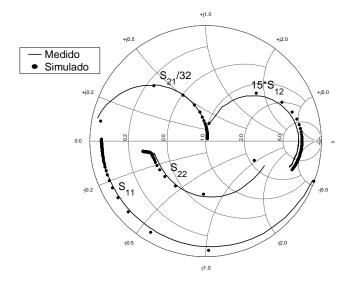

| Figura 59. Elementos intrínsecos calculados polarizando al transistor de 100μm para el diseño de un amplificador altamente eficiente clase E o F                                                            |

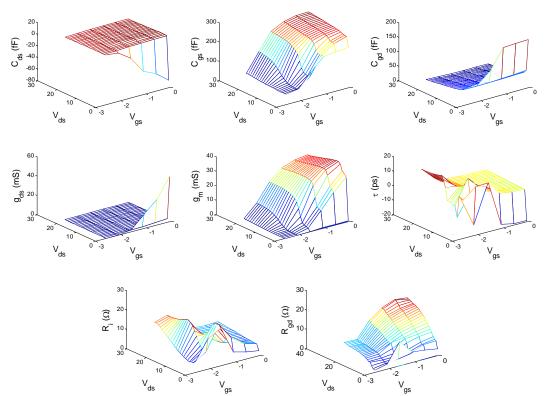

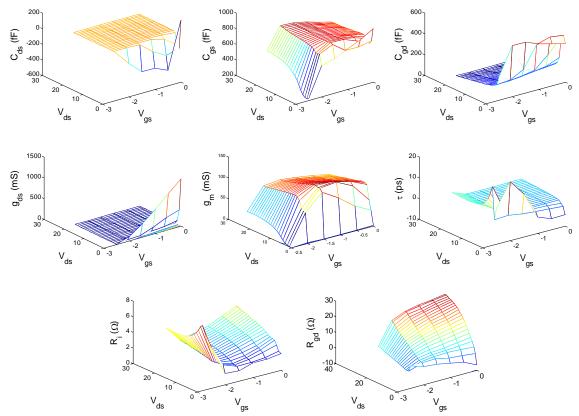

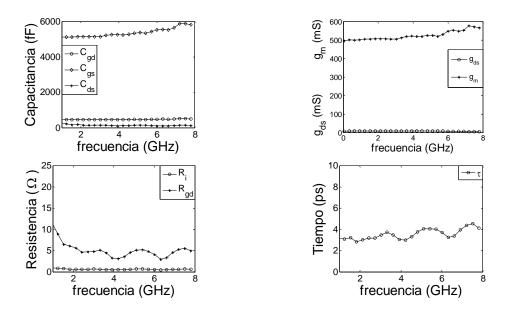

| Figura 60. Gráfica tridimensional de los elementos intrínsecos versus los voltajes de compuerta y drenador del HEMT de GaN de 100 µm                                                                        |

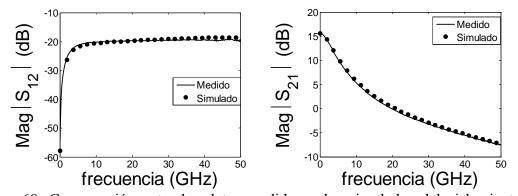

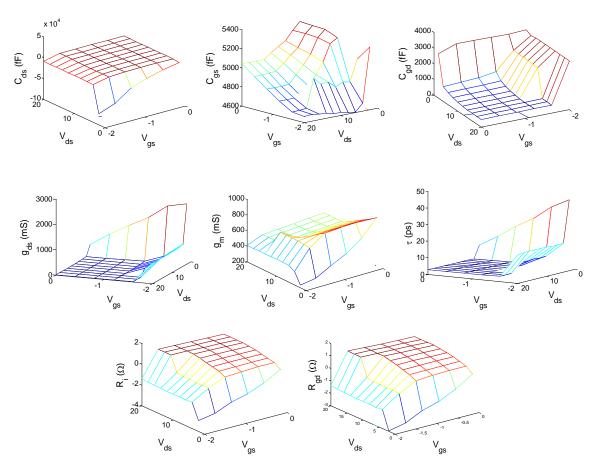

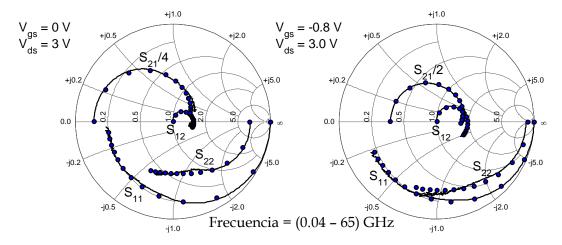

| Figura 61. Comparación entre los datos medidos y los simulados del aislamiento (a) y la ganancia (b) del HEMT de GaN de 100 $\mu$ m polarizado a ( $V_{gs}$ = 0 V; $V_{ds}$ = 20.0 V; $I_{ds}$ = 44.62 mA). |

| Figura 62. Gráfica I(V) del HEMT de GaN de 300 μm y la ubicación de las diferentes polarizaciones para el diseño de amplificadores clase A, B AB, E y F                                                     |

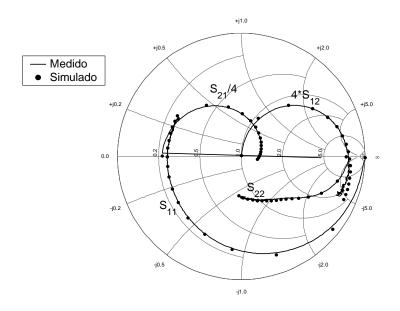

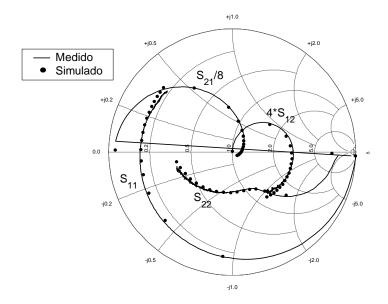

| Figura 63. Comparación de los parámetros S medidos y simulados para el diseño de un amplificador clase A ( $V_{gs}$ = -1.0 V; $V_{ds}$ = 10.0 V; $I_{ds}$ = 123.9 mA)                                       |

| Figura 64. Comparación de los parámetros S medidos y simulados para el diseño de un amplificador clase B, E o F ( $V_{gs}$ = -2.5 V; $V_{ds}$ = 20.0 V; $I_{ds}$ = 19.6 mA) 102                             |

| Figura 65. Comparación de los parámetros S medidos y simulados para el diseño de un amplificador clase AB ( $V_{gs}$ = -0.5 V; $V_{ds}$ = 4.0 V; $I_{ds}$ = 162.3 mA)                                       |

| Figura 66. Elementos intrínsecos calculados polarizando al transistor de 300μm para el diseño de un amplificador altamente eficiente clase E o F                                                            |

| Figura 67. Gráfica tridimensional de los elementos intrínsecos versus los voltajes de compuerta y drenador del HEMT de GaN de 300 µm                                                                        |

| Figura 68. Comparación entre los datos medidos y los simulados del aislamiento (a) y ganancia (b) del HEMT de GaN de 300 $\mu$ m polarizado a ( $V_{gs}$ = 0 V; $V_{ds}$ = 21.0 V; $I_{ds}$ = 191.30 mA).   |

| Figura 69. Gráfica I(V) del HEMT de GaN de 2 mm y la ubicación de las diferentes polarizaciones para el diseño de amplificadores clase A, B, E o F                                                          |

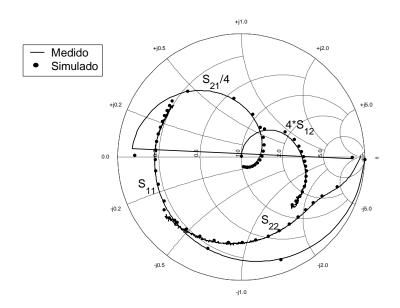

| Figura 70. Comparación de los parámetros S medidos y simulados a una polarización para el diseño de un amplificador clase A ( $V_{gs}$ = -1.0 V; $V_{ds}$ = 10.0 V; $I_{ds}$ = 396.5 mA)                    |

|                                                                                                                                                                                                             |

# Lista de Figuras (continuación)

| Figura 71. Comparación de los parámetros S medidos y simulados a una polarización pel diseño de un amplificador clase B, E o F ( $V_{gs}$ = -2.0 V; $V_{ds}$ = 18.0 V; $I_{ds}$ =                                   |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 65.31 mA).                                                                                                                                                                                                          |      |

| Figura 72. Elementos intrínsecos calculados polarizando el transistor de 2mm para el diseño de un amplificador altamente eficiente clase E o F                                                                      | 106  |

| Figura 73. Gráfica tridimensional de los elementos intrínsecos versus los voltajes de compuerta y drenador del HEMT de GaN de 2mm                                                                                   |      |

| Figura 74. Comparación entre los datos medidos y los simulados del aislamiento (a) y ganancia (b) del HEMT de GaN de 2mm polarizado a $(V_{gs} = -2.0 \text{ V}; V_{ds} = 1 \text{ V}; I_{ds} = 65.31 \text{ mA}).$ | 8.0  |

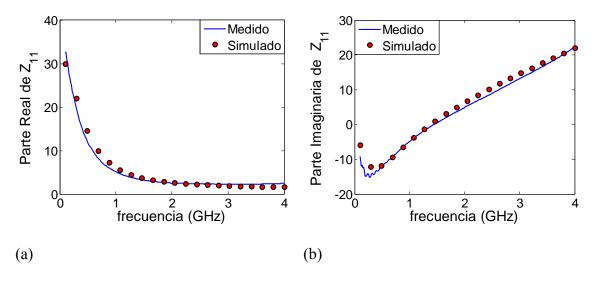

| Figura 75. Simulación de la parte real (a) y la parte imaginaria (b) de $Z_{11}$ del cold FET directa de un HEMT de InP ( $I_{gs} = 1 \text{ mA}$ ).                                                                |      |

| Figura 76. Simulación de los parámetros Y del cold FET en pinchoff de un HEMT de                                                                                                                                    | InP. |

| Figura 77. Comparación de los parámetros S medidos y simulados de un HEMT de Inl<br>bajo dos condiciones de polarización diferentes                                                                                 | P    |

| Figura 78. Simulación de la parte real (a) y la parte imaginaria (b) de $Z_{11}$ del cold FET directa de un MESFET de GaAs ( $I_{gs} = 0.5 \text{ mA}$ ).                                                           | en   |

| Figura 79. Simulación de los parámetros Y del cold FET en pinchoff de un MESFET of GaAs.                                                                                                                            | de   |

| Figura 80. Comparación de los parámetros S medidos y simulados de un MESFET de GaAs bajo dos condiciones de polarización diferentes.                                                                                |      |

| Figura 81. Simulación de la parte real (a) y la parte imaginaria (b) de Z <sub>11</sub> del cold FET directa de un HEMT de SiC (I <sub>gs</sub> = 1 mA).                                                            | en   |

| Figura 82. Simulación de los parámetros Y del cold FET en pinchoff de un HEMT de                                                                                                                                    | SiC. |

| Figura 83. Comparación de los parámetros S medidos y simulados de un HEMT de Sig                                                                                                                                    |      |

| bajo dos condiciones de polarización diferentes                                                                                                                                                                     |      |

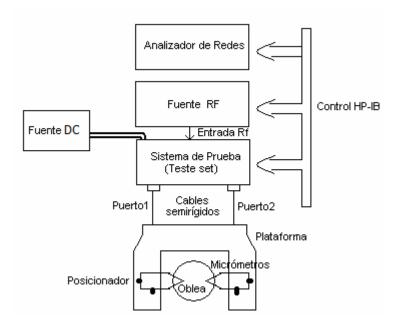

| Figura A1 Sistema de caracterización para "obleas"                                                                                                                                                                  |      |

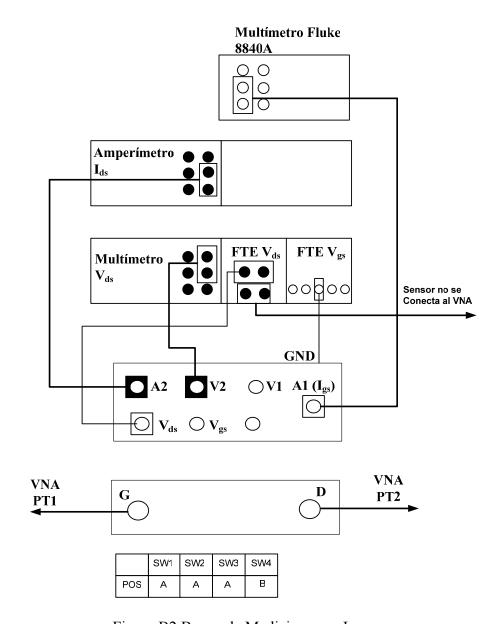

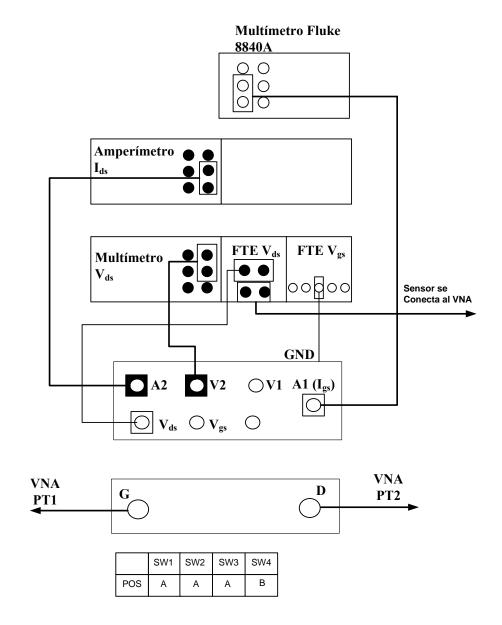

| Figura B1 Banco de Mediciones en Directa                                                                                                                                                                            |      |

| Figura B2 Banco de Mediciones en Inversa                                                                                                                                                                            |      |

| Figura B3 Banco de Mediciones a diferentes puntos de polarización                                                                                                                                                   |      |

### Lista de Tablas

| Tabla I. Ventajas del GaN sobre otros materiales.                                         | . 14 |

|-------------------------------------------------------------------------------------------|------|

| Tabla II. Elementos parásitos extraídos para transistores de AlGaN/GaN de diferentes      |      |

| longitudes de compuerta.                                                                  | . 88 |

| Tabla III. Comparación de las capacitancias parásitas calculadas para los transistores de |      |

| AlGaN/GaN.                                                                                | . 94 |

| Tabla IV. Error entre los parámetros S medidos y simulados                                | 108  |

| Tabla V. Elementos parásitos extraídos para transistores de diferentes tecnologías        | 114  |

### Capítulo I.

### Introducción

#### I.1 Antecedentes.

unque los dispositivos de estado sólido han remplazado en parte a electrónica de vacío en la mayoría de los sistemas electrónicos de microondas a través de los últimos 30 años, la revolución no ha terminado. En particular, los tubos de microondas siguen dominando las áreas de alta potencia de RF para microondas y ondas milimétricas en aplicaciones de radar y en la transmisión de comunicaciones. Asimismo, se ha mejorado la capacidad de producir niveles adecuados de potencia de RF a frecuencias mayores a los 100 GHz, y la capacidad de los dispositivos para operar a temperaturas mayores a los 250 °C. El desarrollo de materiales y dispositivos de estado sólido en estas áreas representa el estado del arte en la electrónica de semiconductores. En estas áreas, los dispositivos de estado sólido no han sido capaces de competir con los dispositivos de tubos al vacío, y la mayoría de los dispositivos que deben entregar niveles de potencia del orden de kilo a megawatts son diseñados utilizando varios tipos de tubos de microondas.

Actualmente los dispositivos de estado sólido producen niveles de potencia de RF menores a los 100 W en la banda S y operan con una potencia de salida de RF razonable en el orden de 1 W, para frecuencias en el rango de los 100 GHz. La tecnología de combinación de potencia y selección de fase permite que la salida de varios dispositivos de estado sólido se combine produciendo una potencia de salida de RF significativamente mejorada y así, en la

práctica, los sistemas de estado sólido pueden competir con sistemas de tubos al vacío en términos de potencia de RF de salida.

Existe un gran interés en mejorar el desarrollo de dispositivos de estado sólido. El incrementar la potencia de RF del dispositivo simplificaría enormemente las técnicas de combinación de potencia y permitiría reducir el costo y tamaño de los transmisores para aplicaciones en sistemas de telecomunicaciones y radar (Trew R.J., *et al.*, 2005).

Avances en la tecnología para semiconductores de banda prohibida amplia, ofrecen la promesa de producir dispositivos electrónicos de microondas con capacidad de manejar potencia de RF un orden de magnitud mayor que el máximo disponible fabricado de semiconductores estándar, tales como el silicio (Si) y el arseniuro de galio (GaAs). Se espera encontrar una amplia gama de aplicaciones de estos dispositivos debido a su alta confiabilidad, tamaño pequeño y su potencial bajo costo ofrecido por la electrónica de estado sólido. Los dispositivos más prometedores son los transistores de efecto de campo (FETs) fabricados de heterounión de AlGaN/GaN. El gas de dos dimensiones (2DEG) que es producido en la heterounión tiene una alta densidad de carga ( $\eta_{ss}\sim 10^{13}~\text{cm}^{-2}$ ), alta movilidad electrónica ( $\mu_n \sim 1500~\text{cm}^2/\text{V-s}$ ), y alta velocidad de saturación ( $\nu_s \sim 2~\text{x}~10^7$ cm/s). Esto permite que un transistor de heteroestructura de efecto de campo (HFET) produzca una alta corriente de RF. Además, los materiales semiconductores basados en nitruro de galio (GaN) tienen un alto campo eléctrico de ruptura crítico, permitiéndoles operar a altos voltajes. El producto de alta corriente y alto voltaje resulta en una operación para altas potencias de RF.

Las redes inalámbricas de banda ancha se encuentran por todas partes. Se ha pronosticado que los transistores de GaN mejorarán estas tecnologías y muchas más.

Estos transistores de GaN resisten un calor extremo y son capaces de manejar frecuencias y niveles de potencia mucho más altos de los manejados con la tecnología de silicio (Si), arseniuro de galio (GaAs), carburo de silicio (SiC) o cualquier otro semiconductor fabricado. Las capacidades de manejo de frecuencias y potencias grandes pueden hacer la diferencia en amplificadores, moduladores y otros componentes clave de las redes de comunicaciones avanzadas, lo cual revitalizaría este sector de la tecnología. La esperanza es que la gente tendrá a su disposición flujos de datos de alta velocidad usando sus celulares, asistentes personales digitales, PC's portátiles o cualquier otra consola de bolsillo capaz de transmitir o recibir video o sonido de alta calidad.

Es difícil de imaginar como los amplificadores de una estación base celular soportarán el diluvio de información de un mundo en el cual cualquiera puede descargar video en cualquier momento y en cualquier lugar. A estos amplificadores ya se les ha llevado a sus límites. Utilizan tecnología de silicio que es sólo 10% eficiente, lo que significa que el 90% de la potencia que se introduce al transistor es desperdiciada en forma de calor. De manera continua, se debe expulsar este calor por medio de potentes abanicos, los cuales se deben equipar por una compleja circuitería que corrija los efectos armónicos y otras distorsiones en el amplificador.

Los transistores de GaN pueden duplicar o triplicar la eficiencia de amplificadores de estación base, de tal manera que un área dada puede ser cubierta por menos estaciones base o, mejor dicho, será más fluida con mayor información a mayores tasas de velocidad. Se liberará de los abanicos y de la circuitería de corrección; incluso será posible disminuir una estación base entera al tamaño de un diminuto refrigerador, lo cual se podría colocar en un

poste de electricidad, en lugar de ocupar un costoso espacio en la oficina central de la compañía de teléfonos.

Esas mismas características de velocidad, manejo de alta potencia y resistencia de calor harían que los transistores se ajusten a una incontable cantidad de usos (Eastman Lester F. y Mishra Umesh K., 2002).

#### I.2 Objetivo.

El objetivo de este trabajo de tesis es desarrollar la metodología teórico-experimental para modelar en pequeña señal por medio de un circuito eléctrico equivalente, los transistores de potencia del tipo FET construidos en tecnología de nitruro de galio (GaN).

#### I.3 Planteamiento del Problema.

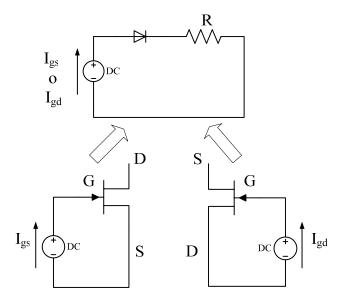

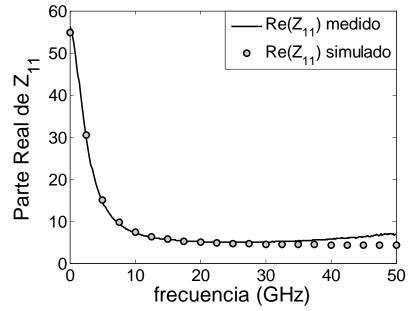

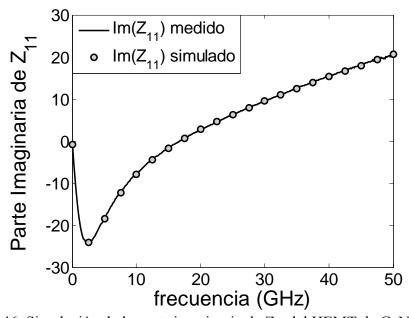

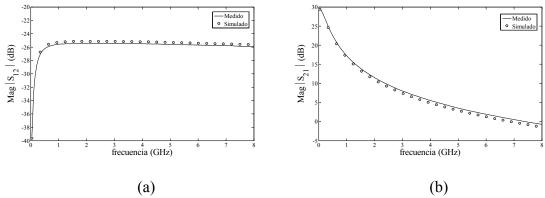

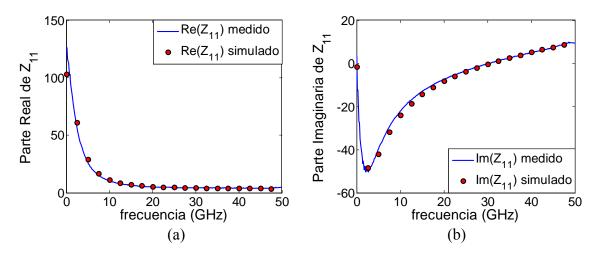

El principal problema en el modelado de transistores de GaN recae en la extracción de los elementos parásitos; principalmente en la dificultad para determinar los elementos  $R_g$ ,  $L_g$  y las capacitancias  $C_{pg}$  y  $C_{pd}$ . El método clásico para extraer los elementos parásitos se basa en la aplicación de una fuerte corriente de DC en directo en la compuerta, hasta que el efecto capacitivo en el parámetro  $S_{11}$  desaparece y entonces, fácilmente se extrae el valor de  $R_g$  y  $L_g$  a partir de los parámetros Z. Sin embargo, en los transistores de nitruro de galio el aplicar una fuerte corriente en la compuerta puede provocar que se destruya el diodo Schottky. En la Figura 1 se muestra como al aumentar considerablemente la corriente de compuerta en un HEMT de AlGaN/GaN el efecto de la resistencia diferencial de compuerta no pudo ser suprimido como en el HEMT de AlGaAs/GaAs. El transistor de GaN se dañó debido a la alta corriente en directo aplicada a la compuerta.

Figura 1. (a) y (b) Parte real e imaginaria de los parámetros Z del cold-FET de un HEMT de AlGaAs/GaAs. (c) y (d) Parte real e imaginaria de  $Z_{11}$  de un HEMT de AlGaN/GaN.

### I.4 Metodología de Investigación.

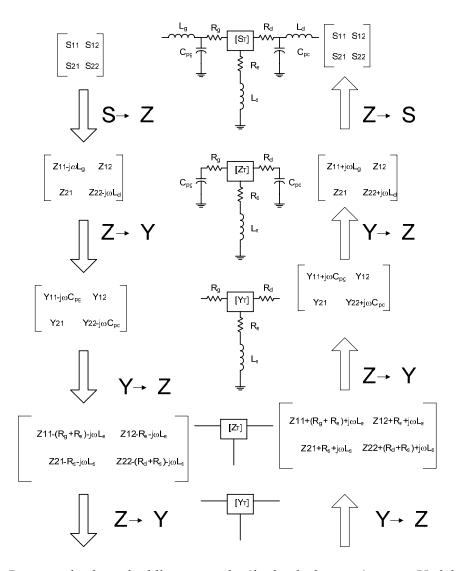

En el siguiente diagrama a bloques se muestran los pasos seguidos como metodología para este trabajo, los cuales son explicados con mas detalle a través de los capítulos que conforman esta tesis.

#### I.5 Organización de la Tesis.

En base a la metodología presentada, esta tesis está organizada de la siguiente manera: En el Capítulo II se presentan las propiedades físicas, funcionamiento, ventajas sobre otros materiales semiconductores y aplicaciones de los transistores fabricados a base de GaN. En el Capítulo III se explica la importancia del modelado de transistores y se estudian los métodos existentes tanto para el cálculo de los elementos parásitos como para el cálculo de los elementos intrínsecos del circuito equivalente del transistor, así como las desventajas de cada uno de estos métodos al aplicarlos en transistores a base de GaN. En el Capítulo IV se presenta un nuevo método para el cálculo de la resistencia e inductancia parásitas de

compuerta  $R_g\ y\ L_g$  en el que se modela el diodo Schottky presente en la compuerta del transistor. También, se desarrolla una nueva metodología para el cálculo de las capacitancias parásitas C<sub>pg</sub> y C<sub>pd</sub>. Además, se resuelven diferentes problemas que se pueden presentar en la extracción de los elementos parásitos, como el cálculo de la resistencia de drenador R<sub>d</sub> cuando esta no es constante en todo el ancho de banda medido, y se muestra el procedimiento a seguir cuando la inductancia de fuente L<sub>s</sub> es menor a cero, como en el caso de algunos transistores coplanares. En el Capítulo V se muestran los resultados obtenidos de la extracción, tanto de los elementos parásitos como de los elementos intrínsecos del modelo de circuito eléctrico equivalente del transistor los cuales validan al método propuesto en esta tesis. Se comparan los datos experimentales con los simulados y se analiza la diferencia entre el método presentado en esta tesis y los métodos existentes para el cálculo de las capacitancias parasitas. Por último, se hace una conclusión sobre los resultados obtenidos tanto de los elementos parásitos como de los intrínsecos. Finalmente, en el Capítulo VI se presentan las conclusiones generales, así como las aportaciones de esta tesis. Además, se proponen líneas de investigación como continuación a este trabajo.

### Capítulo II.

#### Material Semiconductor de Nitruro de Galio

#### II.1 Características de los Transistores de AlGaN/GaN.

demás de tener una conductividad térmica cerca de siete veces mayor a la de GaAs, el GaN tiene un alto campo de ruptura y por consecuencia soporta altos niveles de potencia. Por otra parte, gracias a sus excelentes propiedades de transporte eléctrico de la heteroestructura AlGaN/GaN, los transistores amplifican a altas frecuencias.

El campo de ruptura de avalancha de un semiconductor es la fuerza del campo, en mega volts por centímetro (MV/cm), necesaria para disparar lo que es conocido como ruptura de avalancha. La condición ocurre cuando el campo es lo suficientemente fuerte para liberar más y más electrones y huecos de los átomos del cristal del semiconductor. Finalmente, cuando una gran cantidad de electrones y huecos han sido liberados de los átomos, la corriente a través del semiconductor aumenta, hasta destruir el semiconductor.

Un alto campo de ruptura es deseado porque significa que el dispositivo semiconductor puede soportar mayores voltajes en dimensiones menores. Un transistor de efecto de campo (FET), por ejemplo, podría tolerar un voltaje mayor, y ese voltaje, junto con una corriente mayor, se traduciría en una mayor densidad de potencia para el dispositivo.

El nitruro de galio tiene un campo de ruptura de alrededor de 3 MV/cm, siendo mayor que los 0.4 MV/cm del arseniuro de galio. Por otro lado, el carburo de silicio también tiene un

campo de ruptura de alrededor de 3 MV/cm, sin embargo, carece de las características favorables de transporte eléctrico del nitruro de galio (Eastman Lester F. y Mishra Umesh K., 2002).

Un alto campo de ruptura, es un indicativo de una banda prohibida ancha. La banda prohibida de un semiconductor es una medida de la cantidad de energía que se requiere para mover un electrón de la banda de valencia a la banda de conducción. En algunos semiconductores, cuando un electrón cae desde la mayor banda de conducción de energía a la banda de valencia causa la emisión de luz. Entre más ancha sea la banda prohibida, mayor será la energía y en consecuencia la frecuencia del fotón emitido. Este hecho explica porque el nitruro de galio, con una de las mayores bandas prohibidas de todos los semiconductores, puede emitir luz color verde, azul, púrpura e incluso ultravioleta.

La banda prohibida del nitruro de galio es tan ancha, que de hecho, el material es transparente, muy parecido al diamante. Fotones a cualquier frecuencia del espectro visible tienen energías que son menores a la banda prohibida del GaN, así que simplemente pasan a través del material sin ser absorbidos. Esto explica porqué los LEDs de GaN azules y verdes son claros como el agua.

El mayor provecho que se puede obtener del nitruro de galio es que combina el alto campo de ruptura del carburo de silicio con las características de alta frecuencia del arseniuro de galio, silicio-germanio, o fosfuro de indio.

La libertad con la que se mueven los electrones en un semiconductor depende típicamente de dos factores, conocidos como la movilidad del electrón y la velocidad de saturación.

La movilidad está determinada por la velocidad con que se mueven los electrones en el material bajo la influencia de campos eléctricos relativamente débiles (por ejemplo, el

causado por un voltaje aplicado). La velocidad de saturación, por otro lado, se refiere a la máxima velocidad que los electrones son capaces de alcanzar bajo la influencia de un campo relativamente fuerte. La movilidad del electrón en el nitruro de galio es menor que en el arseniuro de galio, pero la velocidad de saturación, alrededor de  $1.3 \times 10^7 \text{ cm/s}$ , es equivalente y debe de alcanzar los  $2 \times 10^7 \text{ cm/s}$  en los siguientes años (Eastman Lester F. y Mishra Umesh K., 2002).

Pero en el caso inusual del nitruro de galio, esos números no empiezan a contar toda la historia acerca de la movilidad del electrón. Cuando se crece nitruro de aluminio-galio sobre una capa de un cristal similar, tal como el nitruro de galio, se forma una heterounión entre los dos cristales diferentes. Esta heterounión es la mayor contribución a la gran característica de alta frecuencia del nitruro de galio.

Dentro del cristal de nitruro de galio, como en cualquier cristal similar, los átomos individuales están cargados electrónicamente o ionizados y los átomos de galio y nitrógeno están arreglados irregularmente los unos con respecto a los otros, debido a la diferencia de tamaño. Esta combinación de ionización e irregularidades lleva a polarización eléctrica espontánea dentro del cristal, o a una separación de carga en incontables, regulares y espaciados átomos positivos y negativos.

En un cristal ordinario de GaN, la polarización no se acumula, debido a que las regiones cargadas de manera opuesta se cancelan. Pero esta cancelación no ocurre donde el GaN termina repentinamente, por ejemplo, en la heterounión con otro cristal tal como el nitruro de aluminio-galio. En ese caso, el cambio abrupto en la interfaz aumenta a una región eléctricamente cargada en la vecindad inmediata del límite. Esa región, cargada y

polarizada, es además aumentada por una polarización piezoeléctrica, la cual surge de la tensión producida por los dos cristales diferentes.

Estas polarizaciones combinadas, en cambio, inducen un exceso de electrones libres en el nitruro de galio. Los electrones se concentran cerca de la región de polarización fuertemente contra el nitruro de aluminio galio, pero sin desviarse dentro de este, debido a que la mayor banda prohibida del material actúa como barrera.

Así, un gas bidimensional de electrones de transporte de carga se forma espontáneamente, muy cerca del límite con el nitruro de aluminio-galio.

#### II.2 Estado del Arte.

El HEMT de AlGaN/GaN demuestra un excelente comportamiento en RF. La alta densidad de carga resultante por la incorporación de aluminio en la capa de AlGaN permite que se obtenga una alta corriente del canal. Los primeros HEMTs fueron fabricados en substratos de zafiro, pero en trabajos recientes se ha enfocado en el uso de substratos de SiC de tipo p. Además, la mayoría de los HEMTs de AlGaN/GaN son fabricados con capas epitaxiales de AlGaN y GaN no dopadas (Trew R.J., *et al.*, 2005).

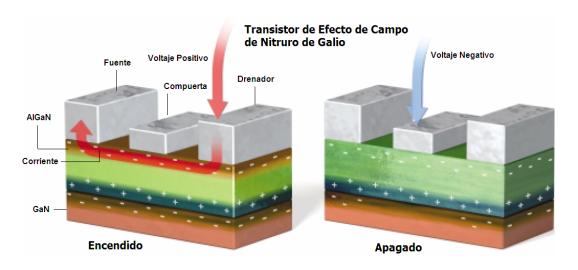

Figura 2. Configuración del HEMT de AlGaN/GaN.

En la Figura 2 se muestra como se hace crecer nitruro de aluminio-galio (AlGaN) dopado con silicio sobre el GaN. El AlGaN tiene una banda prohibida mayor a la del GaN. Las impurezas del silicio en el AlGaN donan electrones al cristal, el cual entonces tiende a acumular electrones en las regiones de menor potencial del pozo cuántico, justo debajo de la interfaz de AlGaN/GaN. Esto forma una "capa" de electrones, la cual constituye un gas bidimensional (2DEG). Aquí, los electrones tienen mayor movilidad debido a que están separados físicamente de los átomos donadores de silicio ionizados que residen en el AlGaN.

#### II.3 Ventajas del Material Semiconductor de Nitruro de Galio.

Para que un nuevo material semiconductor sea exitoso, debe tener claras ventajas sobre tecnologías existentes. A menudo el nuevo material debe superar el desempeño de otros materiales, permitir nuevas aplicaciones, o prometer reducciones significativas de costos. La Tabla I muestra algunas propiedades de los semiconductores más importantes (Silicio (Si), arseniuro de galio (GaAs), fosfuro de indio (InP) y los recién emergentes semiconductores de banda prohibida ancha (WBGS) carburo de silicio (SiC) y nitruro de galio (GaN) (Eastman Lester F. y Mishra Umesh K., 2002). Para aplicaciones electrónicas de alta potencia, el valor agregado de WBGS puede ser encontrado mediante la combinación de un alto voltaje de ruptura con una alta velocidad del electrón. Esto es prometedor en la realización de aplicaciones a alta frecuencia y alta potencia, las cuales no pueden ser realizadas en otros sistemas de materiales. Otra ventaja está relacionada con la banda prohibida. Una banda prohibida ancha implica mayores enlaces en el material, haciéndolo menos susceptible a químicos y variaciones de temperatura. Por lo tanto, dispositivos desarrollados utilizando estos materiales pueden ser utilizados en ambientes hostiles.

Tabla I. Ventajas del GaN sobre otros materiales.

| Ventajas del Nitruro de Galio Sobre |                     |         |           |          |         |             |

|-------------------------------------|---------------------|---------|-----------|----------|---------|-------------|

| Otros Materiales Semiconductores    |                     |         |           |          |         |             |

| Semiconductor                       |                     | Silicio | Arseniuro | Fosfuro  | Carburo | Nitruro de  |

| (comúnmente utilizad                | dos)                |         | de Galio  | de Indio | de      | Galio       |

|                                     | T                   |         | (AlGaAs/  | (InAlAs/ | Silicio | (AlGaN/     |

| Característica                      | Unidades            |         | InGaAs)   | InGaAs)  |         | GaN)        |

| Banda Prohibida                     | eV                  | 1.1     | 1.42      | 1.35     | 3.26    | 3.49        |

| Movilidad del                       | cm <sup>2</sup> /Vs | 1500    | 8500      | 5400     | 700     | 1000 - 2000 |

| Electrón a 300°K                    |                     |         |           |          |         |             |

| Velocidad de                        | $X10^7$ cm/s        | 1.0     | 1.3       | 1.0      | 2.0     | 1.3         |

| Saturación pico                     |                     | (1.0)   | (2.1)     | (2.3)    | (2.0)   | (2.1)       |

| Campo de ruptura                    | MV/cm               | 0.3     | 0.4       | 0.5      | 3.0     | 3.0         |

| Crítico                             |                     |         |           |          |         |             |

| Conductividad                       | W/cm*K              | 1.5     | 0.5       | 0.7      | 4.5     | >1.5        |

| Térmica                             |                     |         |           |          |         |             |

| Constante                           | $\epsilon_{ m r}$   | 11.8    | 12.8      | 12.5     | 10.0    | 9.0         |

| Dieléctrica Relativa                |                     |         |           |          |         |             |

#### II.4 Origen de los electrones 2DEG.

Los dispositivos HEMT basados en la tecnología AlGaAs/GaAs tienen canales de conducción formados por una capa de conducción de electrones libres en la heterounión formada por un semiconductor dopado de banda prohibida ancha (AlGaAs) y un semiconductor de banda prohibida, no dopada, más pequeña (GaAs). Los electrones en el borde del AlGaAs dopado se transfieren al semiconductor de menor banda prohibida y se juntan en el pozo cuántico que se forma en el GaAs en la interfaz entre los dos materiales. Los electrones son confinados en el pozo cuántico, el cual tiene un espesor en el orden de

los 20 - 30 Å. La distribución de electrones en el pozo cuántico es esencialmente de dos dimensiones debido a la gran dimensión del canal tanto a lo largo como a lo ancho, y el pequeño espesor del pozo cuántico. Por esta razón se le da el término de gas de electrones de dos dimensiones a la densidad de carga (2DEG) y es caracterizada como una densidad de carga por unidad de área ( $\eta_{ss}$ ) con unidades de cm<sup>-2</sup>. La densidad de carga por unidad de área para la heterounión de AlGaAs/GaAs es del orden de  $\eta_{ss} \sim 2 \times 10^{12} \text{ cm}^{-2}$  (Trew R.J., *et al.*, 2005). La ventaja del 2DEG es que esencialmente no hay átomos de impurezas en el GaAs no dopado ni en el pozo cuántico, y los electrones en el canal de conducción no experimentan una dispersión de impureza significativa, permitiéndoles una muy alta movilidad, generalmente mucho mayor que la que se puede obtener en la mayoría de los materiales semiconductores. La velocidad de portadores es alta, y la resistencia del canal de conducción es muy baja, permitiendo que los HEMTs tengan un buen comportamiento a alta frecuencia y con características de bajo ruido.

Por otra parte, las primeras heteroestructuras de AlGaN fueron fabricadas al crecer capas delgadas de AlGaN en material GaN más delgado. Originalmente ninguna de las capas de AlGaN ni GaN fueron dopadas. Sin embargo, se observó que, a pesar de la falta de electrones del dopado, un 2DEG fue establecido en la heterounión, como se muestra en la Figura 3. El 2DEG tiene una muy alta densidad de carga por unidad de área, del orden de  $\eta_{ss} \sim 10^{13}$  cm<sup>-2</sup>, lo cual es uno de los cinco ventajas del AlGaN/GaN sobre la heterounión de AlGaAs/GaAs.

Figura 3. Banda de conducción de una heterounión de AlGaN/GaN mostrando el pozo quántico y 2DEG.

La pregunta fundamental es: ya que no se introducen intencionalmente átomos de impurezas para suministrar electrones, ¿cuál es la fuente de electrones que forma el 2DEG? Los datos medidos de heteroestructuras fabricadas con una variedad de condiciones de crecimiento siempre producen una alta densidad de 2DEG. Se ha establecido que la densidad del 2DEG varía con la concentración de Al en la capa de AlGaN, obteniéndose una mayor densidad de carga para mayores concentraciones de Al (Trew R.J., *et al.*, 2005). Un argumento válido para la formación del gas bidimensional de AlGaN/GaN puede ser explicado mediante el modelo mostrado en la Figura 4.

Figura 4. Modelo de formación del gas bidimensional en la interfaz AlGaN/GaN.

De acuerdo a este modelo, los electrones que forman el gas bidimensional resultan del proceso de crecimiento. Se sabe que la capa del semiconductor AlGaN es tanto polar como piezoeléctrica. Durante el crecimiento, los átomos del cristal se alinean de tal manera que la parte positiva de las capas atómicas está alineada hacia la capa de GaN. Al incrementarse el espesor de la capa, durante el crecimiento, las capas atómicas continúan alineándose creando un campo eléctrico interno a la capa de AlGaN, con la parte positiva del dipolo frente al GaN y el lado negativo del dipolo frente a la superfície de crecimiento. La magnitud del campo eléctrico es muy alta, del orden de  $E \sim 10^6 \text{ V/cm}$ , y es suficiente para ionizar algunos de los electrones covalentes, así como impurezas que están presentes en el material. El campo eléctrico ionizará electrones y causará que fluyan hacia la interfaz en donde caerán dentro del pozo cuántico, creando así el gas bidimensional. A medida que los

electrones se mueven del AlGaN al GaN la magnitud del campo eléctrico se reduce, actuando de ese modo como un mecanismo de retroalimentación que apaga el proceso de transferencia de electrones. Se establece una condición de equilibrio cuando se transfieren suficientes electrones al pozo cuántico para reducir la magnitud del campo eléctrico en el AlGaN al punto donde no se transfieren más electrones. La concentración de aluminio en el AlGaN se convierte en un control en la densidad del gas bidimensional desde que produce una tensión en la interfaz de AlGaN/GaN que incrementa la densidad de carga polarización/piezoeléctrico, la cual de acuerdo con la ley de Gauss define el campo eléctrico en el AlGaN.

#### II.5 Efectos de Alta Corriente y Limitaciones Carga-Espacio.

Durante la porción del ciclo de RF de alta corriente, la densidad de corriente puede alcanzar valores muy grandes. Por ejemplo, el espesor del pozo cuántico para el canal de conducción en la heterounión del AlGaN/GaN es de alrededor de 25 Å. La corriente medida para estos dispositivos se encuentra en el orden de los 1-1.2 A para un dispositivo de 1mm de ancho. De tal forma que, si todos los electrones fueran confinados al pozo cuántico la densidad de corriente sería del orden de  $J \sim 50 \times 10^6$  A/cm². Los efectos de carga-espacio ocurren cuando la densidad de electrones inyectada es del orden de la carga en el material. Bajo estas condiciones, el campo eléctrico se ve afectado por la carga inyectada de acuerdo a la ecuación de Poisson:

$$\frac{dE}{dx} = \frac{q}{\varepsilon} (N_d - n_o - \partial n) \cong -\frac{q}{\varepsilon} \delta n, \qquad (1)$$

donde la densidad de portadores de corriente en equilibrio  $n_o$ , es esencialmente igual al dopado del material  $N_d$ , y  $\delta n$ , es el exceso de carga inyectada.

El nivel de carga inyectada que producirá perturbaciones en el campo eléctrico escalado con la cantidad de dopado del material. Para un dopado en el material de  $N_d \sim 10^{16}$  cm<sup>-3</sup> la corriente crítica para el comienzo de los efectos de carga espacial es  $J_{sc} \sim 30 \times 10^3$  A/cm<sup>2</sup>, y para  $N_d \sim 10^{19}$  cm<sup>-3</sup>, se incrementa a  $J_{sc} \sim 30 \times 10^6$  A/cm<sup>2</sup> (Trew R.J., *et al.*, 2005).

La densidad de corriente de operación medida en los HEMTs de AlGaN/GaN se encuentra por encima del campo eléctrico para el comienzo de los efectos carga-espacio durante la porción de alta corriente del ciclo de RF. Una vez que ocurren los efectos carga-espacio, la resistencia del semiconductor aumenta muy rápido. Por ejemplo, se ha reportado que al duplicar la corriente se produce un incremento de un orden de magnitud en la resistencia del semiconductor. El efecto de carga-espacio tiene el mayor efecto en la región compuerta-fuente y produce una resistencia de fuente modulada por corriente. El resultado es que la recta de carga dinámica no puede lograr el mayor potencial de corriente indicado en las curvas características I-V. La recta de carga dinámica se modifica a valores de voltaje mayores.

#### II.6 Efectos de Alto Voltaje.

La porción de alto voltaje en el ciclo de RF introduce no linealidades debido al fenómeno de ruptura. Existen dos fenómenos mayores de ruptura que afectan el rendimiento del HEMT:

Conducción en inversa de la compuerta debido al alto campo eléctrico en el borde de la compuerta. 2. Ruptura de RF en el canal de conducción debido al alto campo eléctrico que existe a través del dominio de la carga.

Es bien sabido que existe un valor elevado de campo eléctrico en el borde de la compuerta debido a la geometría bidimensional de los FET. La magnitud del campo eléctrico en este punto varía con el voltaje aplicado en la compuerta, incrementándose cuando el voltaje de compuerta se aproxima al pinch-off, y además con el incremento del voltaje de drenador. Para altos voltajes de drenador, los cuales ocurren durante la porción de alto voltaje en el ciclo de RF, y para grandes voltajes de compuerta, la magnitud del campo eléctrico en el borde de la compuerta puede fácilmente exceder  $E \sim 10^6 \text{ V/cm}$ . Esto es suficiente para producir una conducción en inversa en la compuerta por un mecanismo conocido como efecto túnel de electrones.

Los electrones que pasan por debajo de la superficie del semiconductor se pueden acumular en la superficie cerca de la compuerta, creando un efecto de "compuerta virtual," donde parece que aumenta la longitud de compuerta con el incremento de la corriente de fuga por el efecto túnel. Bajo estas condiciones, la longitud de compuerta aparenta ser una función dinámica de la RF aplicada, y se incrementa al aumentar la RF. Esto genera un decremento dependiente de la RF aplicada, en la capacidad de manejo de corriente del dispositivo, y una reducción en la  $f_T$  del dispositivo. Los electrones que se acumulan en la superficie debido a las trampas de portadores se mueven lentamente debido a la alta masa efectiva resultante en la superficie de la banda de conducción. Se mueven con baja movilidad y se disipan lentamente. De esta manera, al pasar los electrones a la superficie, la región de deserción debajo de la compuerta es menos capaz de responder a modulaciones rápidas del voltaje de compuerta, introduciendo un retardo de tiempo en el comportamiento corriente-

voltaje y una reducción en el comportamiento a alta frecuencia del dispositivo. Además, la región de deserción debajo de la compuerta produce una barrera electrostática en el camino de los electrones del canal, y debido a que esta barrera no es modulada tan rápidamente, los electrones del canal tienden a ser atrapados en la región compuerta-fuente. La carga atrapada aumenta el efecto carga-espacio e incrementa la resistencia de fuente cuando la corriente excede la condición de corriente limitada por la carga espacial (Trew R.J., et al., 2005). Además, bajo la aplicación de campos altos, los electrones pueden pasar de la compuerta al semiconductor con suficiente energía como para producir una ionización de impacto. Cuando esto ocurre, la corriente de compuerta se incrementa y empieza una emisión de luz en el borde de la compuerta. Las características de la conducción en inversa del electrodo de compuerta son un factor importante en la determinación del comportamiento en saturación del dispositivo cuando opera bajo condiciones de pequeña señal.

El efecto de fuga en la compuerta puede reducirse enormemente con la aplicación de la tecnología ""field-plate"". Al aplicar la técnica "field-plate" se suprime el campo eléctrico en el borde de la compuerta, y de ese modo se reduce la corriente de fuga significativamente. Esta tecnología es utilizada tanto en MESFETs y HEMTs de GaAs como en HEMTs de AlGaN/GaN. La tecnología "field-plate" permite la aplicación de grandes voltajes de drenador; se han aplicado voltajes de drenador del orden de  $V_{ds} = 30$ - 40~V para FETs de GaAs, y  $V_{ds} = 120~V$  para HEMTs de AlGaN/GaN. Esto, por supuesto, permite que se desarrollen voltajes de RF muy altos a través del dispositivo y que se genere una potencia de salida de RF alta.

#### II.7 Modo de Operación.

El FET ordinario de silicio tiene tres terminales llamadas fuente, compuerta y drenador. La compuerta está separada del substrato subyacente por medio de un aislante delgado. En el tipo de dispositivo más común, un voltaje positivo aplicado a la compuerta crea una región bajo el aislador con varios electrones en movimiento. Esta región, en consecuencia, permite el paso de corriente entre la fuente y el drenador. Entre mayor sea el voltaje de compuerta, podrá haber una mayor cantidad de corriente de drenador-fuente.

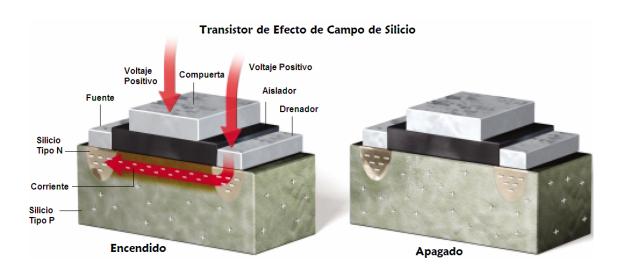

Figura 5 Modo de operación de un FET de Silicio.

Por otro lado, en el FET de GaN, el gas electrónico bidimensional ya existe naturalmente. Así que un voltaje positivo aplicado en el drenador genera inmediatamente una corriente de la fuente al drenador. Así, la cantidad de corriente varía al aplicarle un voltaje negativo a la compuerta, la cual restringe el número de electrones para fluir de la fuente al drenador. Un voltaje negativo lo suficientemente grande elimina totalmente el flujo de corriente. Así, en

contraste con el FET de silicio, el cual se encuentra normalmente apagado, el FET de GaN se encuentra normalmente encendido.

Esto nos lleva a otra característica única del FET de GaN: no requiere de impurezas no dopadas. El gas de portadores móviles puede ser creado en la mayoría de los otros semiconductores solamente al doparlos con impurezas para permitirles un exceso de electrones o huecos.

Figura 6 Modo de operación de un FET de GaN.

Se ha demostrado que los amplificadores de potencia de microondas fabricados con estos dispositivos ofrecen un comportamiento superior de potencia de salida de RF, particularmente a temperaturas elevadas, comparados con componentes fabricados de FETs (MESFETs) de metal semiconductor a base de GaAs o transistores de Si. Se espera que estos dispositivos encuentren aplicaciones en fuentes de RF y amplificadores de potencia para transmisores de las estaciones base empleadas en sistemas de telefonía celular, en

transmisores de satélite, en transmisores de HDTV, módulos de potencia para radares de selección de fase, radares de vigilancia y control de tráfico y otras aplicaciones. Los dispositivos son particularmente muy atractivos en aplicaciones donde se requiere una operación a altas temperaturas. Sin embargo, antes que el potencial de estos dispositivos esté disponible, se deben de resolver los problemas que esta tecnología presenta actualmente en RF.

#### II.8 Aplicaciones.

Casi todas las primeras investigaciones en dispositivos de banda ancha (WBGS) fueron dirigidas hacia aplicaciones optoelectrónicas. Esto se debió al hecho de que el azul era el único color faltante en el mercado de los diodos emisores de luz (LED). Antes de que el GaN estuviera disponible, el SiC fue utilizado, pero su banda prohibida indirecta resultó en eficiencias pobres. Usando la aleación de nitruro de aluminio galio indio (InGaAlN) se pueden realizar LEDs altamente eficientes con longitudes de onda variando desde ultravioleta al azul/verde.

LEDs basados en GaN pueden ser utilizados, en conjunto con LEDs amarillos y naranjas fabricados utilizando el sistema de materiales de fosfuro de Indio, Galio y Aluminio (AlGaInP), para realizar pantallas de televisión a todo color empleando LEDs. Otras numerosas aplicaciones son posibles incluyendo semáforos, iluminación automotriz, y posiblemente iluminación en general. Los LEDs blancos se han realizado al aplicar una capa de fosfuro dentro de un LED ultravioleta. Como en la luz tubular, esto convertirá al fotón ultravioleta en luz visible.

Los dispositivos optoelectrónicos a base de GaN representan un mercado multimillonario pero aún existen varios problemas por resolver. Los más importantes están relacionados con el dopado del material tipo p y la obtención de espejos con cavidades de alta reflectividad. Este proceso es difícil porque los materiales dopantes, la mayoría de magnesio (Mg), tienen una alta energía de activación.

La mayor parte del desarrollo de WBGS para aplicaciones electrónicas está dirigido hacia dispositivos de alta potencia y frecuencia. Se ha demostrado una impresionante potencia del orden de 4-6 W/mm a 4 GHz para MESFETs de SiC y de 10-11 W/mm a 10 GHz para AlGaN/GaN HEMTs (Jacobs Bart, 2004). Los HEMTs basados en GaN muestran usualmente una mejor operación a alta frecuencia debido a las altas movilidades que se pueden lograr en estas estructuras. Tanto el SiC como el GaN ofrecen la ventaja de una alta densidad de potencia y buenas propiedades térmicas, lo cual puede resultar en módulos más pequeños con menos requerimientos de enfriamiento. Además, si se usan voltajes de alimentación mayores, las impedancias de entrada y salida aumentan considerablemente, lo cual reduce la complejidad del acoplamiento de impedancias. Recientemente se han desarrollado HEMTs basados en GaN los cuales entregan 20 W. Estos dispositivos son diseñados para aplicaciones en sistemas universales de comunicaciones móviles (UMTS). Una gran parte de las investigaciones para aplicaciones electrónicas en WBGS está relacionada con la industria militar. En Estados Unidos, la oficina de investigación naval (ONR) está activamente involucrada en la coordinación y financiamiento de programas de investigación llevados a cabo en varias universidades. Una de las aplicaciones que se les quiere dar a estos dispositivos es la creación de un amplificador de banda ancha para radares multifuncionales. Este sistema podría disminuir el área total de arreglos de radares

que podrían ser aprovechados por los adversarios y así eludir un posible conflicto electromagnético entre diferentes arreglos y reducir los costos totales. Otro ejemplo es un amplificador de bajo ruido (LNA), el cual es más robusto debido al alto campo de ruptura y a su buena conductividad térmica. Se han publicado dispositivos con figuras de ruido bajas del orden de 0.6 dB a 10 GHz y puntos de intersección de intermodulación de tercer orden 10 dB mayores que para aquellos amplificadores basados en GaAs.

Otra área de aplicación es la electrónica de alta temperatura. Usualmente, los sistemas electrónicos que controlan y monitorean dispositivos de alta temperatura, como el motor de un jet, están localizados en áreas de enfriamiento. Esto requiere alambrado entre el sistema electrónico y los sensores. Si estos sistemas pudieran ser instalados en el área de alta temperatura, la cantidad total de alambrado podría reducirse. La degradación del cableado ha sido la mayor causa de tragedias de la aviación. WBGS tiene que competir con las tecnologías de Si de baja potencia y de Si aislante (SoI), que son utilizadas actualmente para aplicaciones a temperaturas mayores a 300 °C. Por tanto, el valor agregado para los WBGS se encuentra en el rango de 300 – 600 °C. La razón para que estos dispositivos se introduzcan en este mercado está relacionada al hecho de que pueden soportar estas temperaturas y la oxidación asociada. Se espera que el mercado total para la electrónica de alta temperatura alcance los \$900 millones de dólares para el año 2008. Se ha estimado que el mercado total de dispositivos electrónicos de GaN alcance los \$500 millones de dólares a finales de esta década. Sin embargo, la economía de escala en el mercado de la optoelectrónica, así como las mejoras en el material y en el crecimiento del substrato en esta área, podrían acelerar la industrialización de dispositivos electrónicos en base a GaN.

# Capítulo III.

# Modelado de Transistores

### III.1 Importancia del Modelado de Transistores.

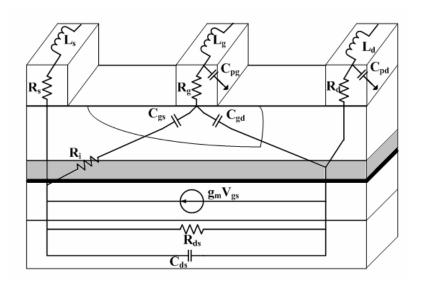

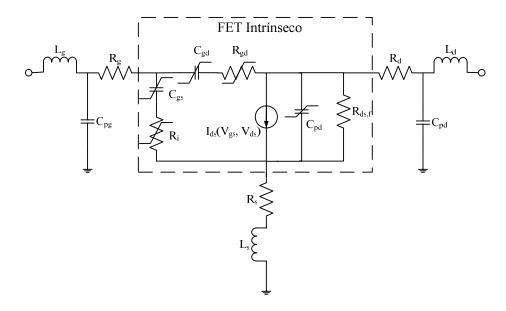

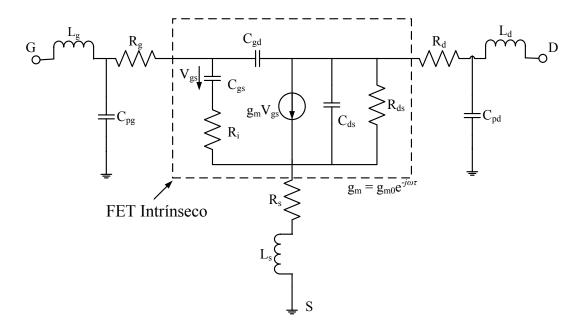

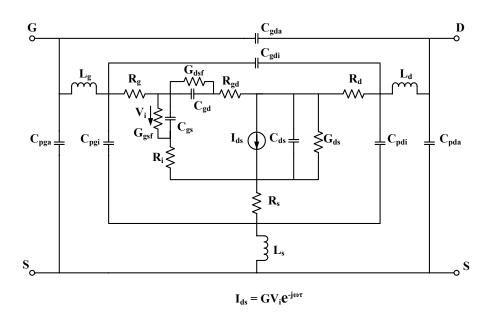

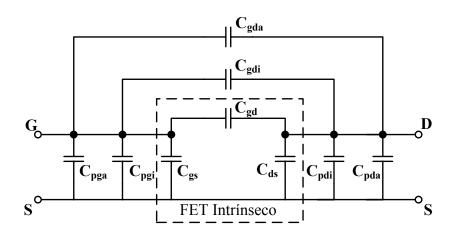

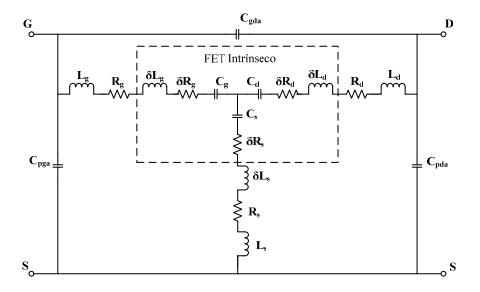

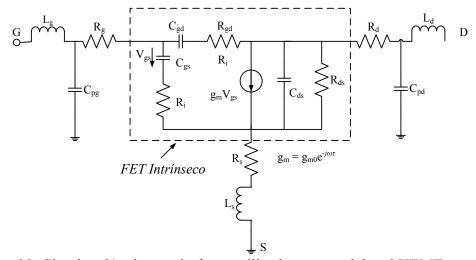

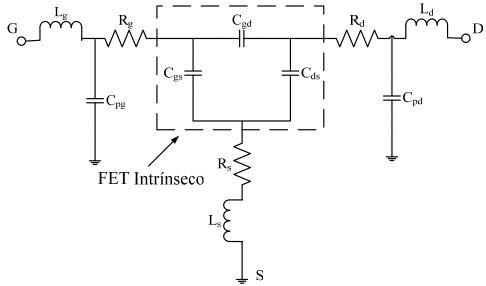

El modelo de circuito eléctrico equivalente en pequeña señal de los transistores de efecto de campo (FET) es muy importante en el diseño de circuitos de microondas. Estos modelos proporcionan una relación entre los parámetros S medidos y el proceso eléctrico ocurrido en el dispositivo. Cada uno de los elementos en el circuito eléctrico equivalente se aproxima a un elemento de tipo concentrado que se relaciona con algún aspecto físico del dispositivo, como se muestra en la Figura 7 (Loo Yau, 2006).

Figura 7. Ubicación de los elementos del circuito eléctrico equivalente para un transistor de efecto de campo.